工具/软件:Code Composer Studio

您好!

过去、我们使用 TMS320C6678ACYP (器件右上角有一个) 和 SPI 器件 N25Q128A11BSF40F 开发了定制板;BOOTMODE[12:0]引脚设置为以下模式:0101100000110 (从 SPI 引导)。 内核 CLK 为100MHz、DDRCLK 为66、6667 MHz。 我们构建了4块电路板、没有任何问题。

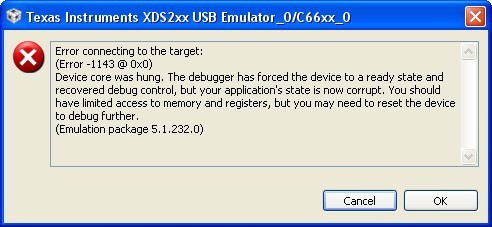

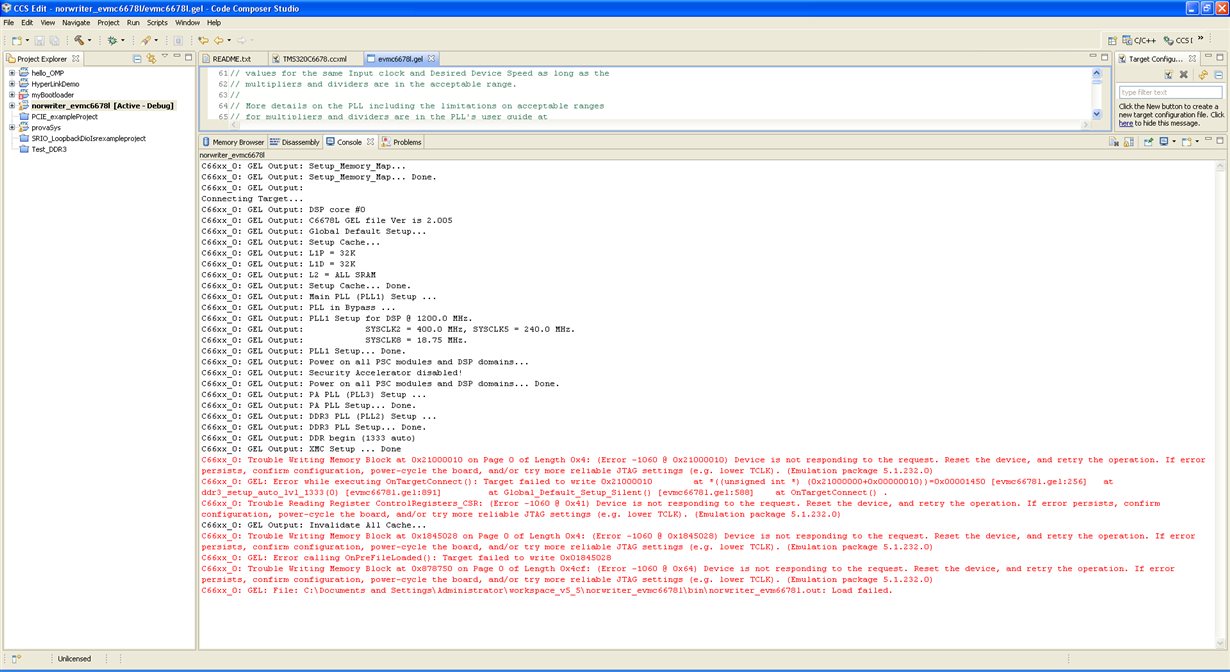

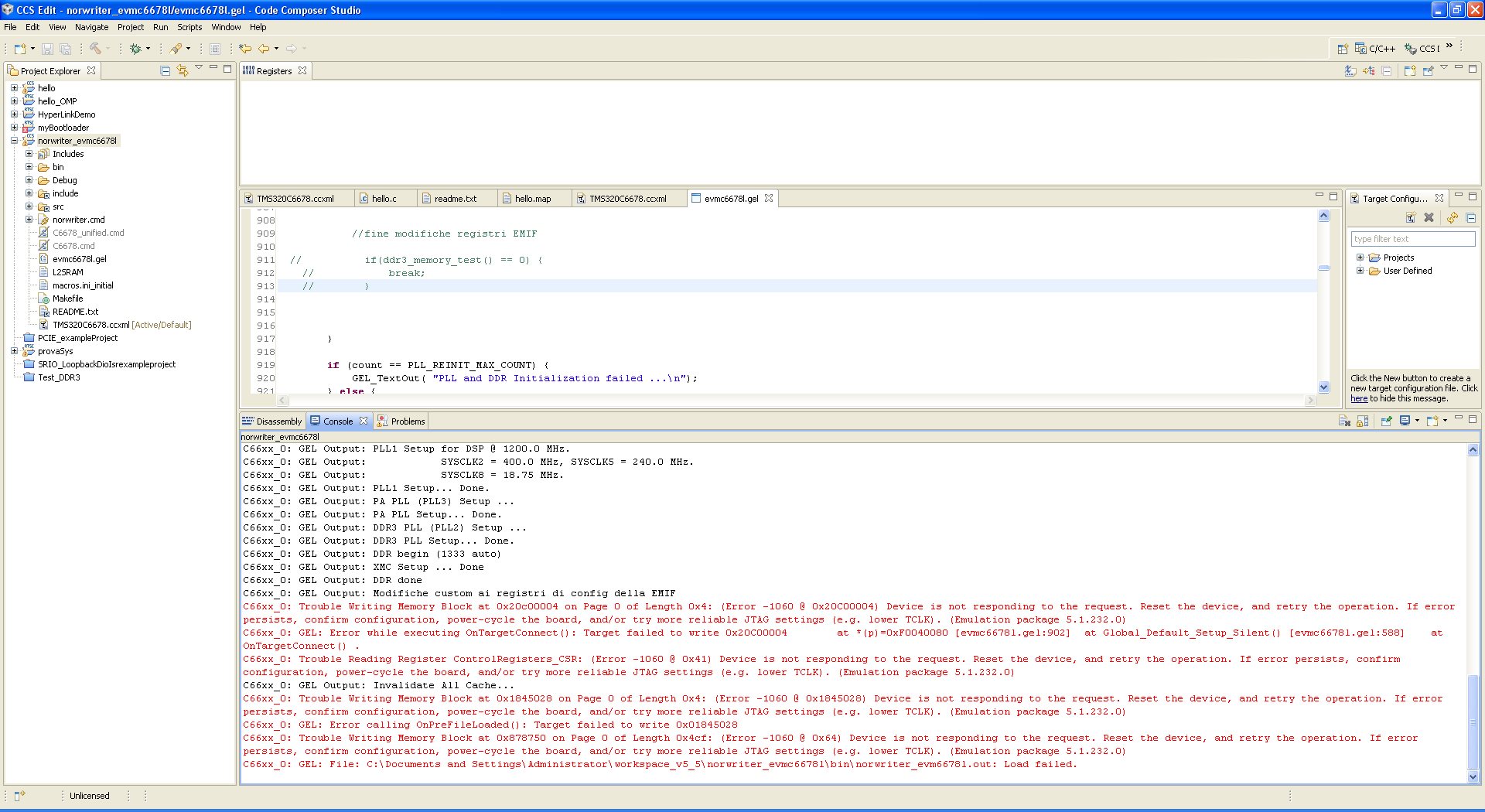

现在、除了 DSP 之外、我们已经重建了另外6块板、与之前的板完全相同、更改为1、25GHz 版本(器件右上角的 A1.25GHZ)。 在这种配置下、我们无法连接 JTAG 仿真器(USB200 JTAG 仿真器)、并显示以下错误:

您对此有什么建议吗?

提前感谢

Fabrizio Gualtieri