主题中讨论的其他器件:TPS22965-Q1、 TPS65919-Q1、

你好。

假设 tda3所有双 vddshv1-6将使用单个3V3供电。

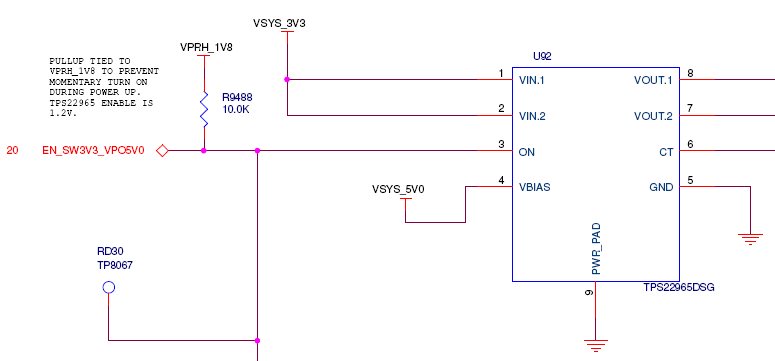

建议将负载开关 TPS22965-Q1用于加电 vddshv。

它具有简单的逻辑。 如果 ON=Lo、则 VOUT (vddshv)=GND、如果 ON=Hi、则 VOUT=VIN (VSYS_3V3)。

我可以看到、出于这一目的、TPS65919-Q1 (OTP=0x52)具有 GPIO3/REGEN1开漏输出(不带内部拉电阻器)。

因此、我几乎不会对该引脚到 VRTC (LDORTC_OUT=1V8)的外部上拉电阻器感到困惑。

您能解释 vddshv 的加电工作流吗?

我可以假设第一级降压(SYS_3V3 OUT)将为22965加电、并且由于 ON 引脚具有上拉电阻、这个开关将输入 SYS_3V3传输到 Vddshv 引脚、与65919上的 LDOVRTC 类似。

稍后将启动919 OTP 并执行 OFF2ACT 序列、因此 REGEN1 (VRTC 开漏) OUT 将为低电平、然后为高电平(SLVUAS4C-Aug16第14页、图7)。

因此、22965 ON 引脚将为低电平、然后为高电平。

由于22965 ON 引脚(65919 REGEN1引脚) 具有外部上拉电阻、是否可以实现 vddshv 初始上升状态?

此致。