尊敬的 TI -专家:

请在以下主题中为我提供帮助、事实上是一个问题。

| 应用描述 |

在 C6414上运行的 DSP 应用(上一个芯片修订版本2.0的 TMS320C6414TCLZ)利用所有三个 McBSP 端口来驱动 EDMA。 以 TDM 模式运行的 McBSP (每个128个时隙)、完全从外部计时。 所有三个 McBSP 的时钟来自相同的源: FPGA 将与外部时钟相同的串行位时钟和帧时钟扩展到所有三个 McBSP。 共享的 EDMA_INT 中断用于所有传输完成(TCC)中断。 在其中、EDMA CIR (中断挂起寄存器)被监控以检测传输完成。 更准确地说、在特定时间(XINT)中断等待全部3个(McBSP)传输完成代码的 TX 和 RX 指示完成。 按照 SPRU234C EDMA 参考指南(第1.15.1段)的建议、ISR 会检查(等待)所有挂起的中断、并继续、直到所有已布置的中断都得到服务。 说到(E) DMA,除了 McBSP 之外,在应用程序中,还只有一个外设也在使用 EDMA: |

| 初始 EDMA 设置 | 传输请求队列 Q1 (3 x McBSP)和 Q2 (HPI)被使用(使用缺省设置的 PQAR 和 TRCTL 寄存器)。 使用元素同步1维传输。 未使用 QDMA。 |

| 问题描述 |

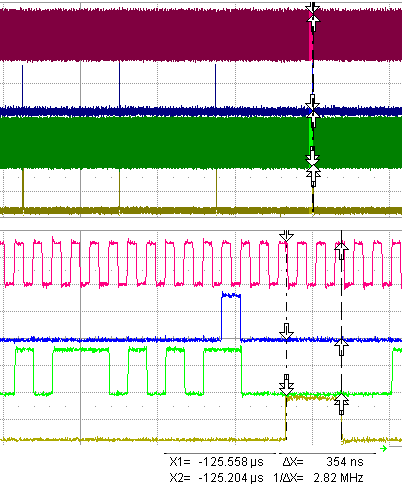

在某些电路板上、随机(6-10次/24小时)完成所有6个 McBSP 传输(所有3个端口的 Rx 和 Tx)所需的时间比通常要长! 在受影响的电路板上、所有三个 McBSP 的 RX 和 TX 传输有时会延迟很长(RX 传输最长)。 |

| 测量值 | 当然、我们已经执行了串行时钟的测量。 在发生问题时和之前的某个时间、不能观察到时钟丢失行为。 |

| 尝试处理此问题 |

由于单个优先级上的请求按顺序连续处理;而不同优先级上的请求可以同时处理、因此我尝试更改 EDMA 队列的用法、以便从并行处理中受益。 我通过以下方式利用 McBSP 的更多队列来更改初始 EDMA 设置: 不幸的是,尽管发生了这些变化,但仍然发生了失败。 |

我的问题:

为了缩小故障范围、我还能做些什么? 什么可能导致该问题?

谢谢!

满载