主题中讨论的其他器件: SN74AVC4T774

我们按照说明编译、加载和使用 C6657 EVM 的 IBL、并能够将应用程序加载到电路板上并启动应用程序。

[ https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1057566/faq-tms320c6657-how-to-flash-the-ibl-intermediate-boot-loader-into-eeprom-and-how-to-flash-the-application-binary-into-nor-how-to-boot-the-ibl-application-binary]

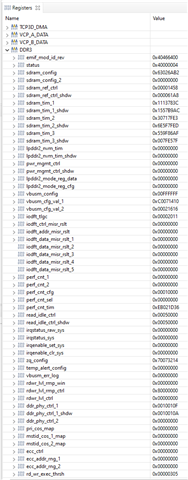

我们现在正在逐步升级到我们自己的定制硬件。 我们的初始硬件具有与 EVM 相似的存储器映射(即 I2C EEPROM、SPI 闪存、DDR3)。 主要区别在于、DDR3存储器需要不同的 DDR3配置设置才能正常运行。

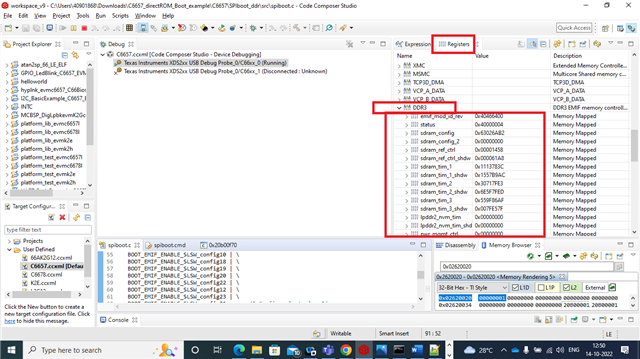

第一步是 修改 EVM GEL 文件以正确配置我们的硬件。 通过这些更改、我们正确配置了 DDR3存储器、并验证了处理器正在运行、并且能够调试应用。

下一步是修改 IBL/RBL 配置以使用这些更改。 我们正在尝试仿真 EVM 的启动特性。 (即从 I2C EERPOM 加载 IBL、并从 SPI 闪存加载应用。) 但是、我们正在努力确定在何处/如何完成此任务。

- 是否有任何文档/应用手册/说明/示例显示了在加载应用之前修改/配置 IBL 以正确配置 DDR3接口的位置/方法?

- 是否可以直接从 SPI 闪存加载 RBL? (即直接从 SPI 闪存引导处理器。) 如果可能、是否有任何文档/应用手册/说明/示例显示在加载应用之前修改/配置 RBL 以正确配置 DDR3接口的位置/方法?

(在某些随机地址停止。)

(在某些随机地址停止。)  (即预期结果)

(即预期结果)

PC 似乎卡在 RBL 中。

PC 似乎卡在 RBL 中。