主题中讨论的其他器件:TDA4VM

尊敬的 TI 团队:

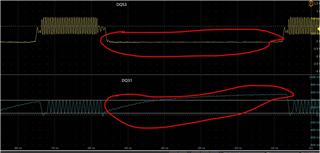

在定制 TDA4VM 中、我们使用的是 Micron 的新 DDR 器件(MT53E1G32D2FW-046 AUT:B)、其中我们看到了以下波形捕获。

通常、在空闲模式下、DQ 应从高电平变为低电平。 如果 DDR 控制器配置不正确、我们会看到此问题。 我已附上用于生成 DDR 配置的 DDR 配置电子表格。 如果需要进一步更改、请查看并告知我们。

e2e.ti.com/.../k3_2D00_j721e_2D00_ddr_2D00_evm_2D00_lp4_2D00_4266_5F00_13_5F00_09_5F00_22.zip

此致、

Chitanya