工具/软件:Linux

尊敬的 TI 团队:

我将使用预构建的映像在 AM5728 IDK 上测试 PCIe 功能。

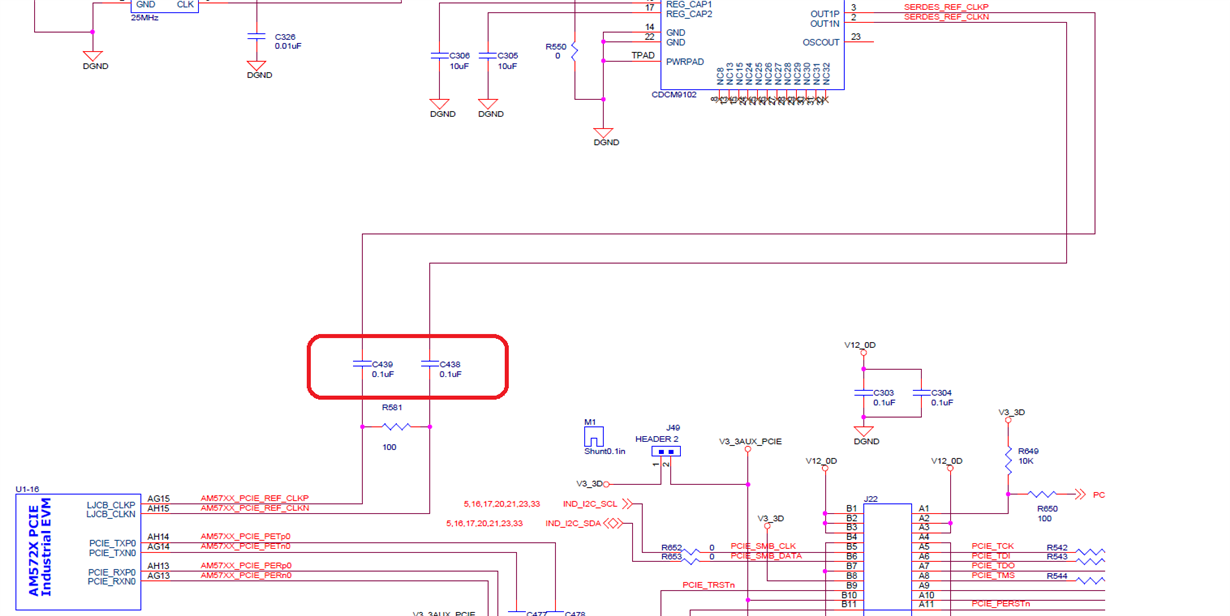

当我删除 C438和 C439时、PCIe 功能在 J22 (PCIe 插槽)上工作正常

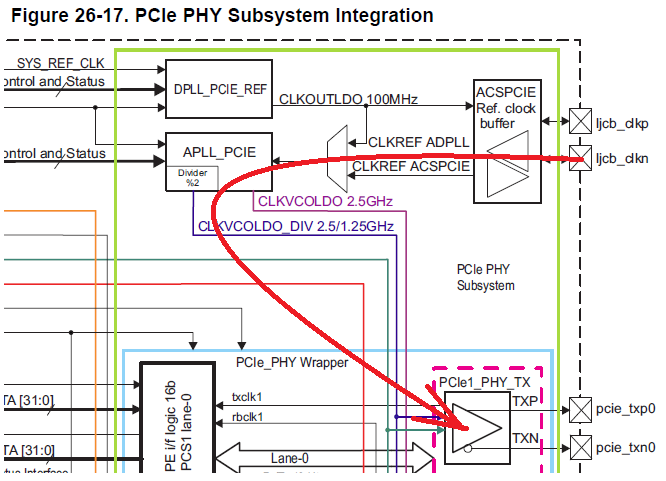

为什么 AM5728 PCIe 不需要外部时钟?

如何从 ljcb_clk 引脚设置 PCIe PHY 时钟?

我认为外部时钟可以改善 PCIe 眼图。

预构建映像:PROCESSOR-SDK-LINUX-AM57X 03.02.00.05

EVM:AM572x IDK (1.3B)