主题中讨论的其他器件:TMDXSK437X

您好!

我在 TMDXSK437X 中看到了 DDR_A0 (N1)线路上的噪声。

由于它的噪声也可以在我们的目标板中看到、我们认为 AM437x 输出了噪声。

a) AM437x DDR 控制器在 A0线路上可能产生输出噪声。 是否为已知问题?

b)我们在目标板上遇到读/写错误。 为了避免这种情况、我们考虑将端接电阻值从50欧姆更改为100欧姆。

您认为它的解决方法是否可能遇到任何其他问题?

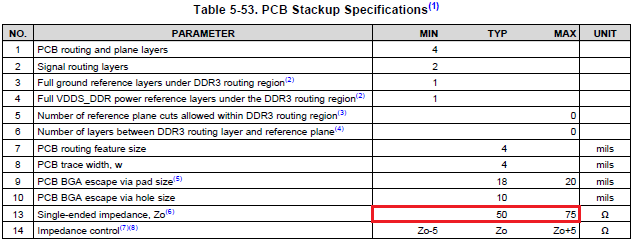

因为数据表将 Zo 指定为典型值50欧姆、最大值为75欧姆。

c)您能否推荐不带终端稳压器的 DDR3L 设计? 这是我们避免读/写错误的另一种权变措施。

此致、RY

DDR_A0 (N1)线路噪声 n TMDXSK437X

AM437x 数据表指定 Zo 为典型值为50欧姆、最大值为75欧姆