工具/软件:Code Composer Studio

我刚刚开始使用 Code Composer 和 TMS320C6748 LCDK、并使用书籍"Real Time Digital Signal Processing from Matlab to C Second Edition"来帮助您开始配置 LCDK 以编写 C 代码。

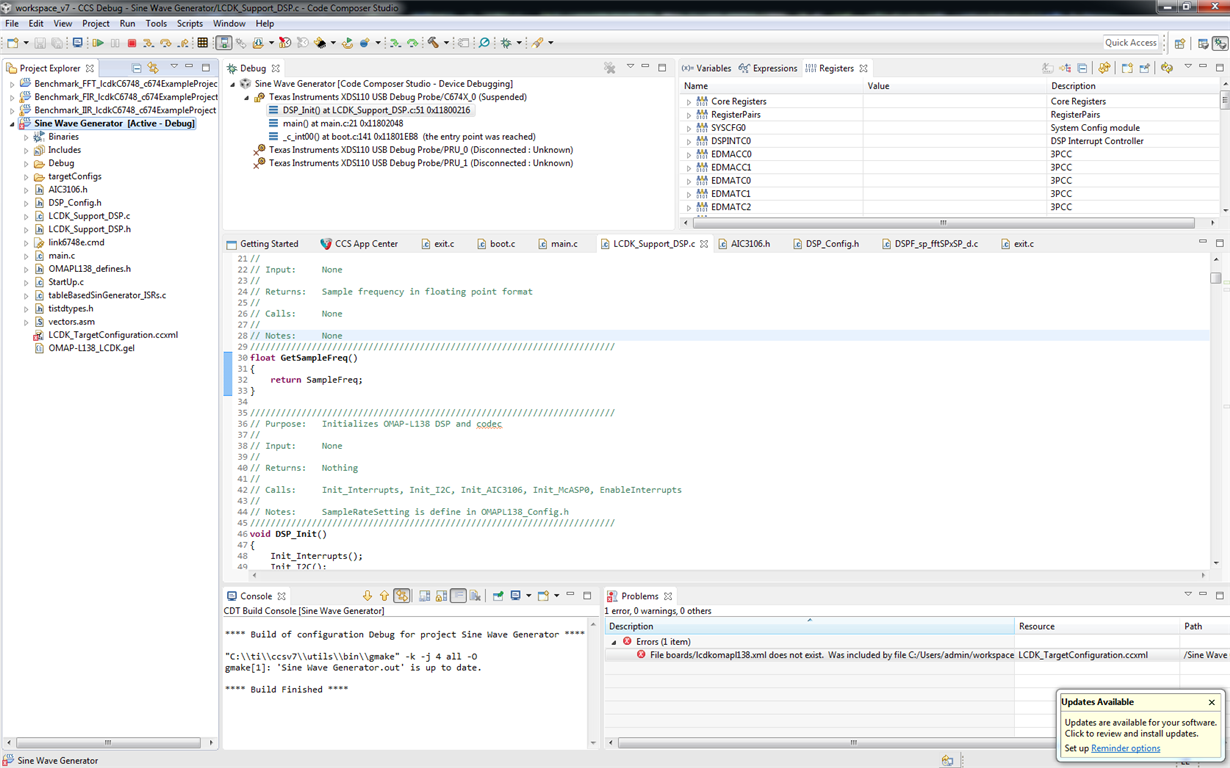

我正在尝试使用他们提供的一些代码来帮助创建正弦波查找表并通过线输出结果。 我有一些问题,但到目前为止,我觉得我对需要做的事情有一个很好的了解。 但是、我的代码在运行、但在尝试初始化 AIC3106音频编解码器时会卡住。

// Welch、Wright 和 Morrow、

//实时数字信号处理、2017

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

//文件名:LCDK_Support_DSP.c

//

概述:支持 OMAP-L138基本初始化的函数

// 硬件资源。

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

#include "DSP_Config.h"

#include "AIC3106.h"

静态浮点 SampleFreq = 0.0F;

//////////////////////////////////////////////////////////////////////////////////////////////////////////////////

//用途:返回

由//确定的当前采样频率 INIT_OMAPL138和 SetSampleRate_AIC3106函数。

//

//输入: 无

//

//返回:浮点格式的采样频率

//

//调用: 无

//

//备注: 无

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

float GetSampleFreq()

{

返回 SampleFreq;

}//////////////////////////////////////////////////////////////////////////////////////////////

////////////////

//用途:初始化 OMAP-L138 DSP 和编解码器

//

//输入: 无

//

//返回:无

//

//调用: init_interrupts、Init_I2C、Init_AIC3106、Init_McASP0、EnableInterrupts

//

//注意: SampleRateSeting 的定义见 OMAPL138_Config.h

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

void DSP_Init()

{

Init_interrupts ();

Init_I2C ();

if (!Init_AIC3106 (SampleRateSeting))){

while (1);//编解码器初始化失败时停止

}

Init_McASP0 ();

EnableInterrupts ();

}

//////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

//用途:初始化 OMAP-L138 DSP 和编解码器以供 EDMA 使用

//

输入: 无

//

//返回:无

//

//调用: init_interrupts_EDMA、Init_I2C、Init_AIC3106、Init_McASP0、EnableInterrupts_EDMA

//

注意: SampleRateSeting 的定义见 OMAPL138_Config.h

////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

void DSP_Init_EDMA ()

{

Init_interrupts_EDMA ();

Init_I2C ();

if (!Init_AIC3106 (SampleRateSetting))){

while (1);//因编解码器初始化失败而停止

我还收到错误"File boards/lcdkomapl138.xml does not exist. 已包含在文件 C:/Users/admin/workspace_v7/Sine 波形发生器/LCDK_TargetConfiguration.ccxml LCDK_TargetConfiguration.ccxml /Sine Wave Generator line 0 problem 中。 但是、我似乎无法解决此错误。

我已经检查了 S1上的开关、它们设置为。

S1=off

S2=开

S3=开

S4=开

S5=off

S6 =关闭

S7=关闭

S8=开

我还附上了我的工作区的图片。