请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMS320C6678 工具/软件:Code Composer Studio

您好、TI 工程师

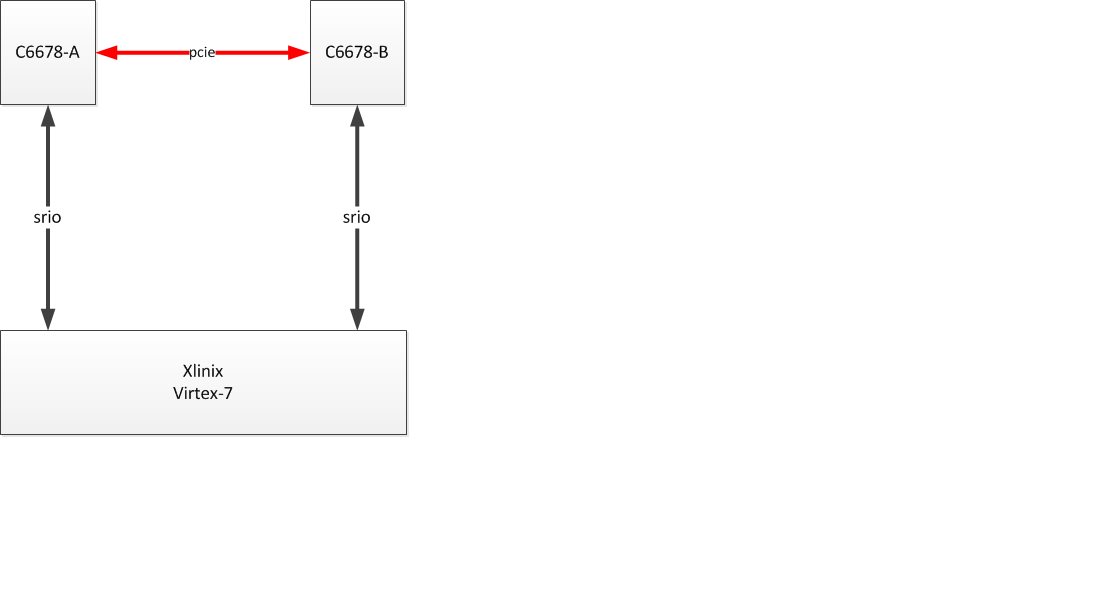

我们在应用中使用 C6678的 SRIO 和 PCIe。有时、这些端口的链路在通电后似乎无法成功建立。 链接如下所示:

配置如下所示:

SRIO:每 通道4个5.0G 波特

每通道 PCIe 2x 5.0G 波特率

错误 描述:

1.对于 SRIO、无法构建 C6678-A/B 和 Virtex-7之间的链路、寄存器0x0290b158保留在0x00000001中;

对于 PCIe、无法构建 C6678 A 和 B 之间的链路。 这样的寄存器:

我们检查 regs cmd_status (0x21800004)和 Debug 0寄存器(0x21801728) ,如下所示:

| 寄存器描述 | C6678-A/B 的值(右侧) | C6678-A 的值(错误) | C6678-B 的值(错误) |

| 命令状态寄存器位3:1 (LOAD_WR_EN IB_XLT_EN OB_XLT_EN) | 0x7 | 0x0 | 0x4. |

| 调试0寄存器 位4:0 LTSSM_STATE | 0x11 | 0x00 | 不稳定,不断变化 |

更多说明:

当这种情况发生时、我只需要重新初始化它、链接将在大多数时间内建立。但我们仍然想知道这是如何发生的、如果我们的代码中有任何不正确的操作。已附加用于初始化端口的代码。您可以检查它。 非常感谢 much.e2e.ti.com/.../pcie-code.txt