工具/软件:TI-RTOS

您好!

我们设计了一个类似于 C6678 EVM 的系统、其中 C6678 DSP 通过 PCIe Gen2 x2连接到 Virtex 7 FPGA。 DSP 计划为根复合体侧。

验证 PCIe 连接所需的步骤如下所示:

- 供应商/子系统供应商 ID

- 器件/子系统器件 ID

- 类代码

- Bar 0内的寄存器偏移量

我们已经成功完成了前3个步骤、但第4个步骤仍然是开放的。

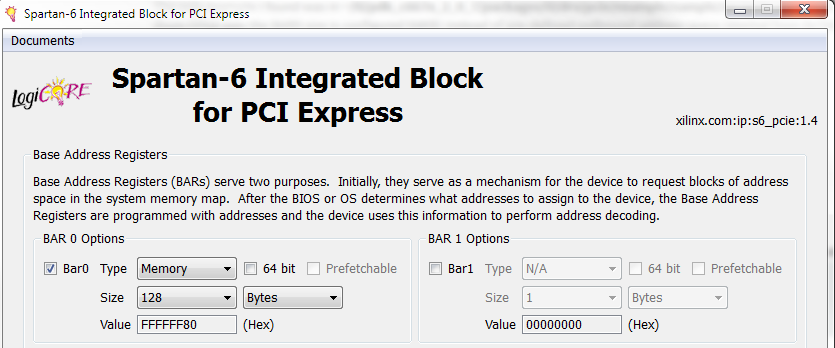

我找到的唯一示例是 在~/ti/pdk_c667x_2_0_7/packages/ti/drv/pcie/example/sample/src/pcie_sample.c 路径中、我不知道如何修改它以读取 BAR0空间寄存器(从 FPGA 端、配置的是64KB 的 BAR0大小)、而不是预定义的出站地址空间(从0x70000000开始)和入站地址空间(从0x90000000开始)。

您能否建议您如何查找所需的示例/修改其来源?

此致

Andranik