团队、

在我们的板上、C6678 DSP 以存储器引导模式工作。 我们将使用 SPI 闪存作为引导源-避免 IBL 的使用。 我们已按照 http://processors.wiki.ti.com/index.php/File:C6678_directROM_boot_examples.zip 步骤生成 SPI 映像、并通过外部编程器将其直接编程到 SPI 闪存中、然后将闪存焊接到电路板上。 之后 、DSP ROM 引导加载 程序会成功配置器件资源以启动引导过程、将映像从 SPI 闪存加载到器件中并停留在 RBL 移交过程中、因此它仍然不执行映像。

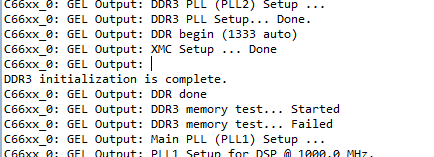

接下来、我尝试通过 C6678 DSP 对 SPI 闪存进行编程、如手册中所述。 我使用 CCS 和 C:\ti\ccsv5\ccs_base\emulation\boards\evmc6678l\gel\evm6678l.gel 作为 电路板 的.gel 文件来连接 到电路板 、但.gel 文件 与 电路板不匹配、DDR3测试失败 、控制台提供了下 一个输出:

在测试时、DSP 读取 它之前写入的不同值。

我尝试根据 SDRAM 器件的数据表(因为它不同于 C6678 EVM 器件)和 http://www.ti.com/lit/an/sprabl2e/sprabl2e.pdf KeyStone I DDR3初始化手册中所述的几何/时序规范、通过 本应用报告中提到的电子表格重新配置.gel 文件、但尚未成功。

请描述 本手册中最关键的步骤、让我更正 .gel 文件、并在我们决定要求您为 您的一侧的电路板计算.gel 文件时为您提供所需的源代码。

P.S.

下面是我们的电路板和 TI C6678 EVM 参考板在 DDR3存储器控制器方面的核心原理图差异:

- 在我们的电路板上、DDRSLRAATE0和 DDRSLRAATE1通道均通过0 Om 电阻器下拉( 未加载1Kom 上拉电阻器)、而在 C6678 EVM 中、DDRSLRAATE0通过2Kom 电阻器下拉、DDRSLRATE1 通过 2Kom 上拉

- 我们板上使用的 SDRAM 部件为 MT41K1G8SN-125 ,而 C6678 EVM 使用 K4B2G1646C-HHHH9。 由于 C6678芯片的勘误表、我们将 DDR3控制器配置为666.67MHz、但 我们板上的 SDRAM 器件是800MHz 速度等级器件

- DDRAM fly-by 问题。

-此注释来自 EVM:地址/命令/控制/时钟路由必须按字节顺序为0、1、2、3 ECC、4、 5、6、7。

-我们板的顺序是0、1、2、3、ECC、7、6、5、4,那么读写水平如何处理这种情况?

请查看此信息、并告知我们 这些差异是否会导致上述测试失败。 其他问题:

- 但我仍然无法理解为什么 DSP RBL 卡在移交过程中、并且当我们通过编程器写入 SPI 闪存时、不会在第一个实验中执行加载的映像

- 我们能否 通过 JTAG 接口直接在 DSP 上执行某些指令而无需 SPI 闪存和 DRAM 交互?