主题中讨论的其他部件:SYSBIOS、 AMIC110、 DP83848M、 EVMK2G、 MATHLIB

工具/软件:TI-RTOS

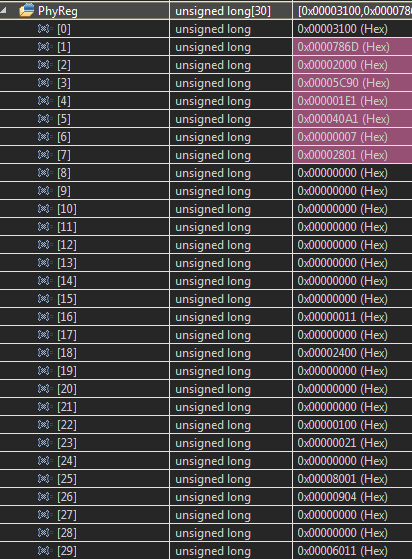

我希望其中一个 EVM 或 Beagle 板上有一个335x 示例项目、该项目使用具有中断功能的 NDK。 我一直在查看 Nimu_BasicExample_bbbAM335x_armExampleProject、但这似乎是为轮询而设置的、但我可能会错。 我在该项目中看不到中断被初始化的任何位置。 我也很不确定大多数设置会做什么、因为我不熟悉 Starterware 和 SoC、TI-RTOS 的文档也很少。

我的主要问题是使从 NDK 到硬件的接口正常工作、我希望我能找到一个示例、因为没有有关如何设置的文档(我找到了)。

我的初始化代码是:

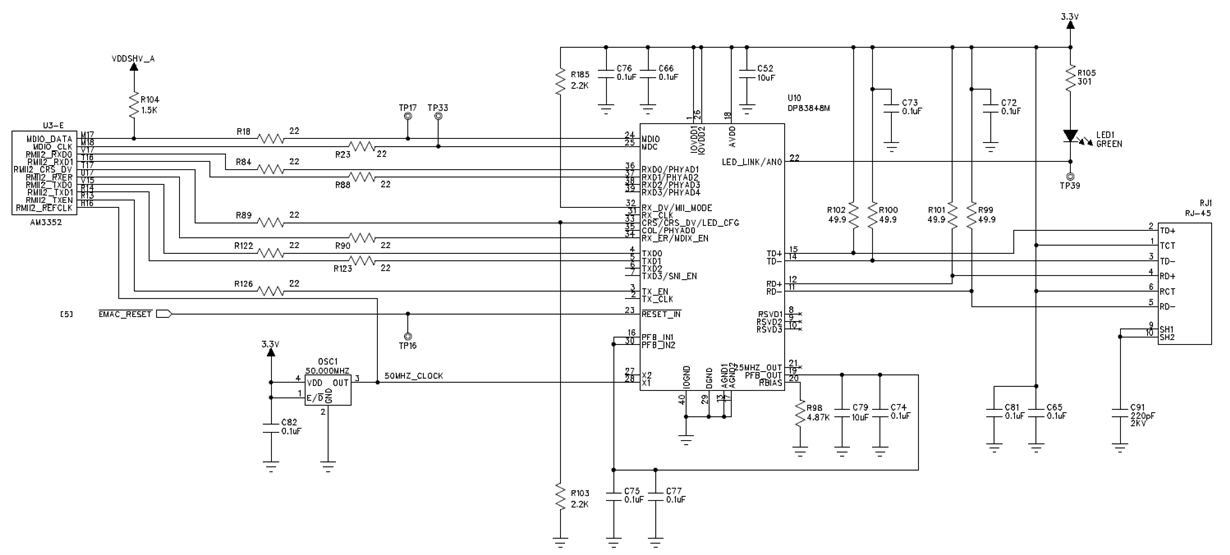

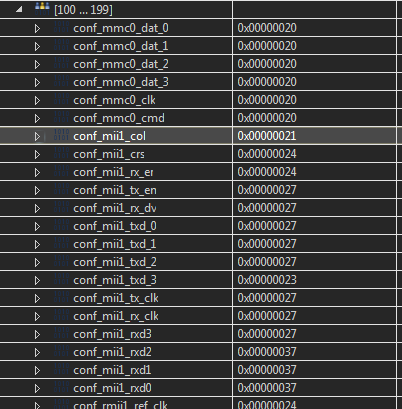

/*芯片配置 MII/RMII 选择*/

SOCCtrlCpswPortMacModeSelect (1、Ethernet_MAC_TYPE_RMII);

SOCCtrlCpswPortMacModeSelect (2、Ethernet_MAC_TYPE_RMII);

EMAC_socGetInitCfg (0、&cfg);

cfg.port[0].phy_addr = EMAC_CPSW_PORT0_PHY_ADDR_UTI;

cfg.port[1].phy_addr = EMAC_CPSW_PORT0_PHY_ADDR_UTI;

cfg.macModeFlags = EMAC_CPSW_CONFIG_MODEFLG_FULLDUPLEX;

EMAC_socSetInitCfg (0、&cfg);

NIMUDeviceTable[NIMU_DEVICE_index++].init =&CpswEmacInit;

NIMUDeviceTable[NIMU_DEVICE_index].init = NULL;

我在 SYSBIOS 中设置了 NDK、它确实会运行。 它检测到电缆已插入、但之后没有任何内容(我希望 DHCP 客户端正在运行、这是因为它会因故障而超时、但网络不响应-是的、网络会执行 DHCP)

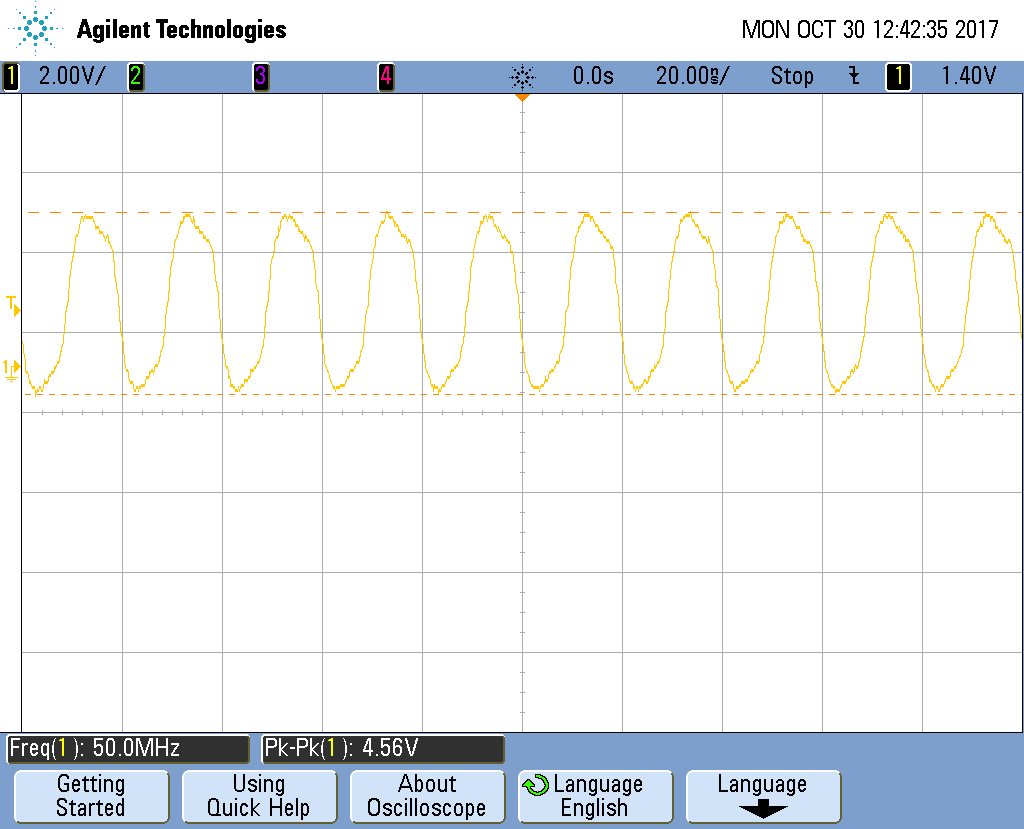

我相信我已经启用了所有时钟。 使用时钟树工具、当您启用模块时、我看到除一个时钟之外的所有时钟都打开、但我不确定在哪里打开250MHz 时钟或如何验证它已经打开。 我不确定哪个寄存器控制它