工具/软件:TI-RTOS

您好!

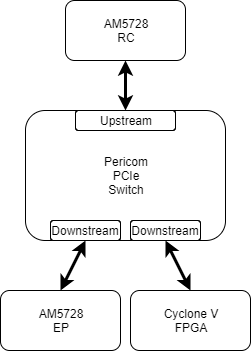

在我们的定制板中、我们有3个端口 Pericom 开关、我们在其中连接了2个 Sitara 处理器和1个 Cyclone V FPGA:

到目前为止、我们在 AM5728上都成功实现了 PCIe 链路。 现在、我要在 RC 上执行 PCIe 枚举。 EP 和 RC 代码都在 C66 DSP 内核内运行。 我理解以下线程中所述的 PCIe 枚举:

我之前在 KeyStone II 器件上实施过此类程序。 在 KeyStone-II 中、我使用了"配置事务设置寄存器"(CFG_SETUP)寄存器来执行该操作。

但是、Sitara 处理器不支持该寄存器。 我已经阅读 了 AM5728 TRM 的第24.9.4.8.2.2节(多次)、但不清楚 如何使用 Pciev1_atuRegionConfig 函数实现这一点。

我们非常感谢您的帮助。

戴维