工具/软件:Linux

我们使用的是 DRA7xx 信息娱乐处理器 J6和 Linux 内核4.4.23。

除了 e2e 帖子:

https://e2e.ti.com/support/arm/automotive_processors/f/1020/p/575710/2259260#2259260

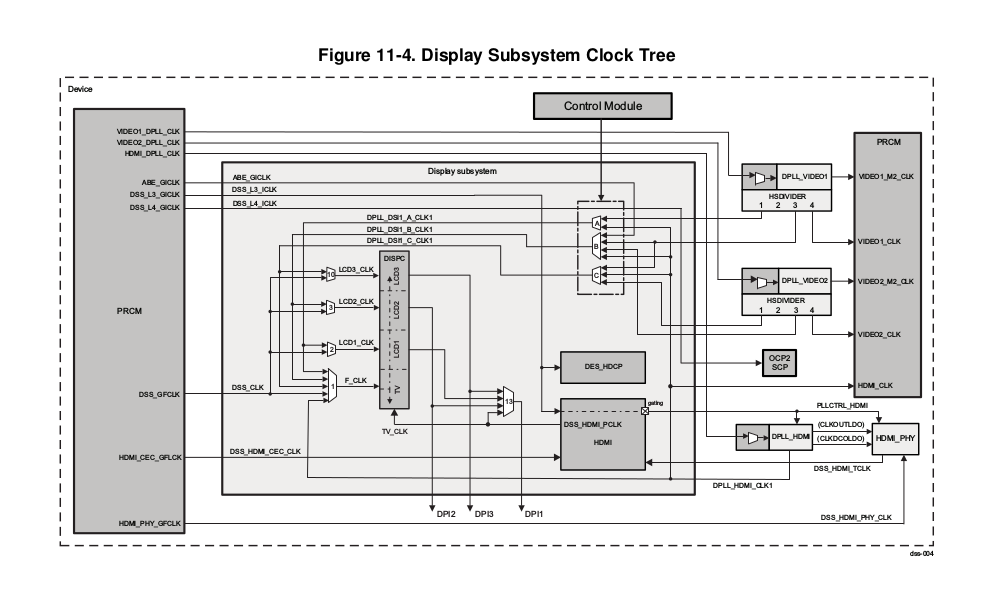

参考图:图11-4. 显示子系统时钟树、请参阅下图。

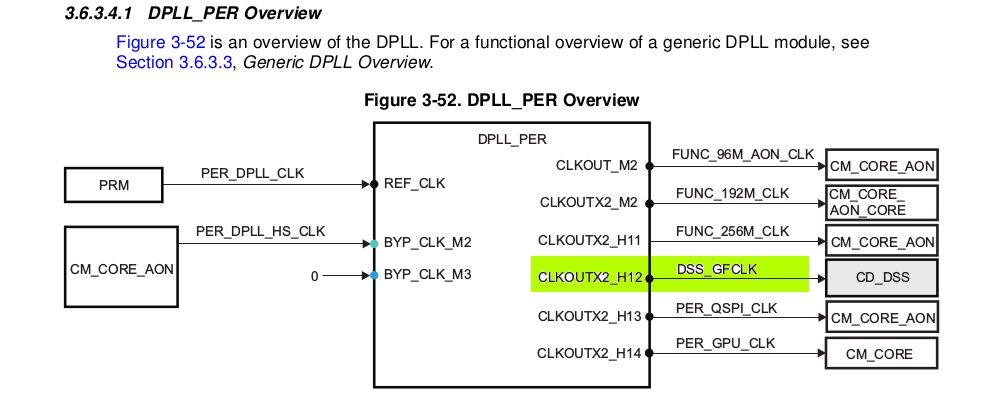

默认情况下、HDMI 驱动程序(在 drivers/GPU/DRM/omapdrm 中)使用此配置:

F_CLK (多路复用器1)由 DSS_CLK (DSS_CLK_SRC_FCK)提供

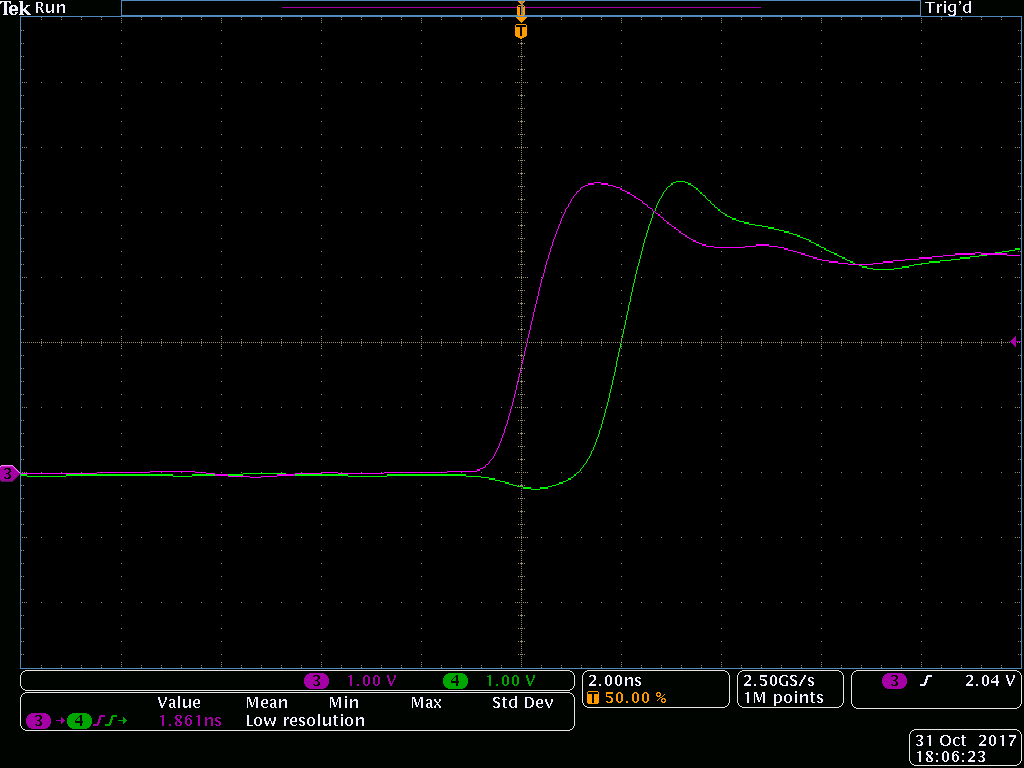

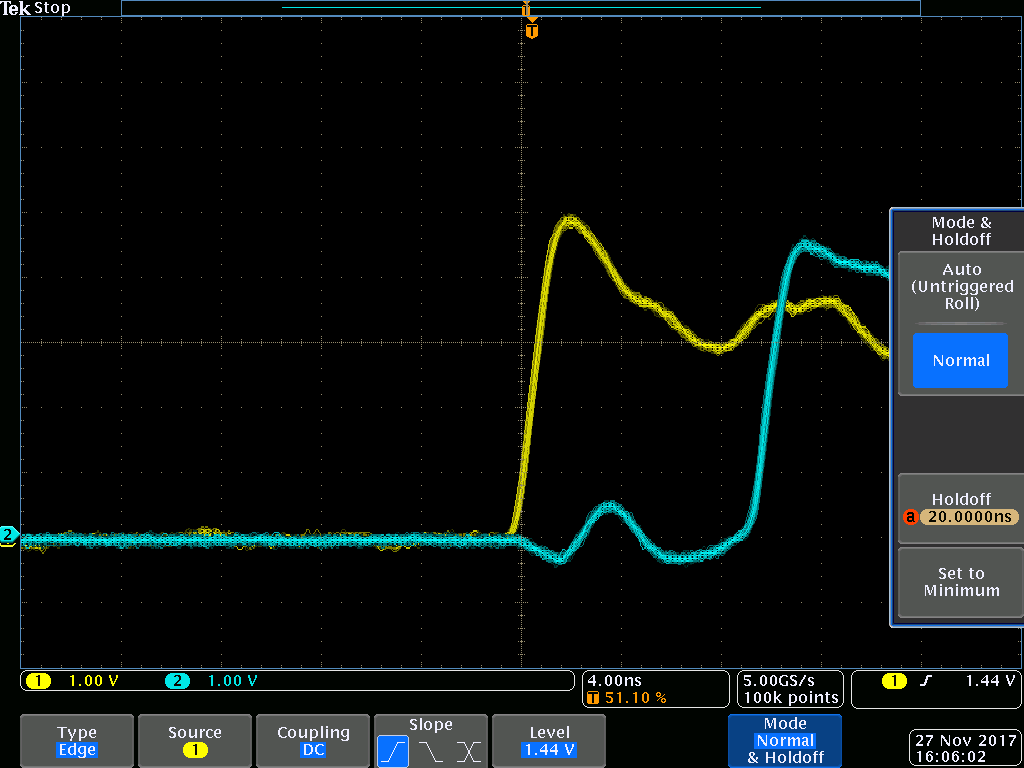

如果我们尝试使用常见的 DSS_CLK 源(而不是来自 DPLL 的视频 PLL 线路)同步 LCD、并在启用显示屏之前引入"热复位"、则2 Vout HSYNC 之间的时间为~2ns (请参阅下面的示波器图)。

但使用这种方法、HDMI 不再起作用。

可以将 HDMI 配置为使用内部生成的时钟、而不是默认的 DSS_CLK?

怎么可能?