工具/软件:Linux

您好!

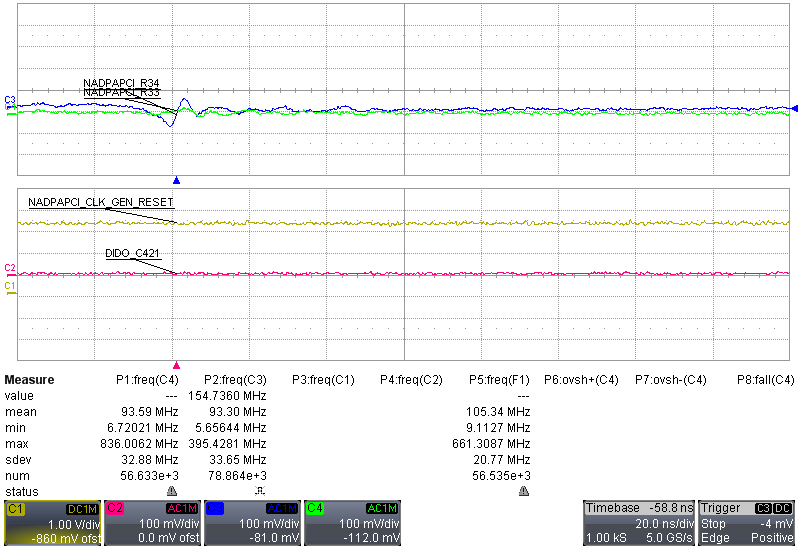

我对基于 TMS320DM8148处理器的客户应用有疑问、我们注意到在尝试从冷温度启动启用 PCI 的内核 Linux (CONFIG_PCI=Y)时出现了问题。

软件在处挂起 while (!(omap_ctrl_readl(TI814X_CONTROL_PCIE_PLLSTATUS) & 0x1)) cpu_relax();

在文件 Linux-OMAP3/arch/arm/mach-omap2/devices.c 中、等待 PCIe PLL 的锁定。

导致此问题的温度可能因每个模块而异、从环境温度降至0°C (此 P/N 的限制温度)。

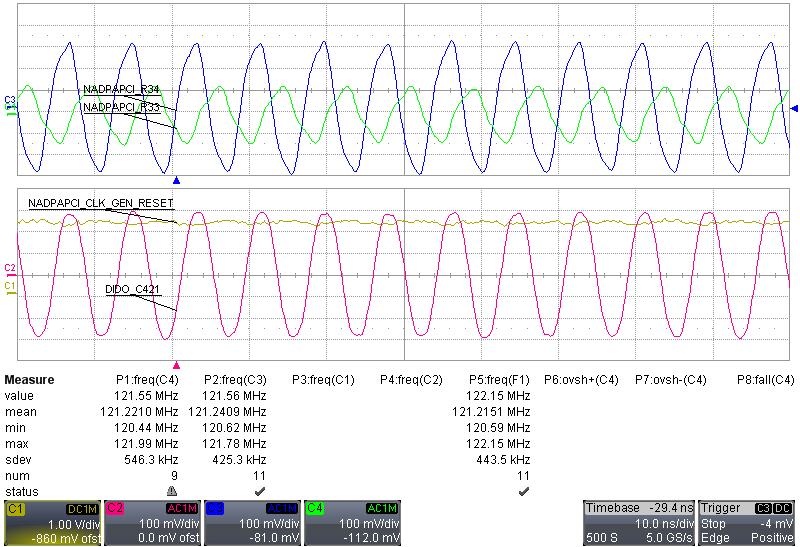

如果我们保持模块通电、它会在几分钟后发生预热并启动、如果达到的温度足够高。

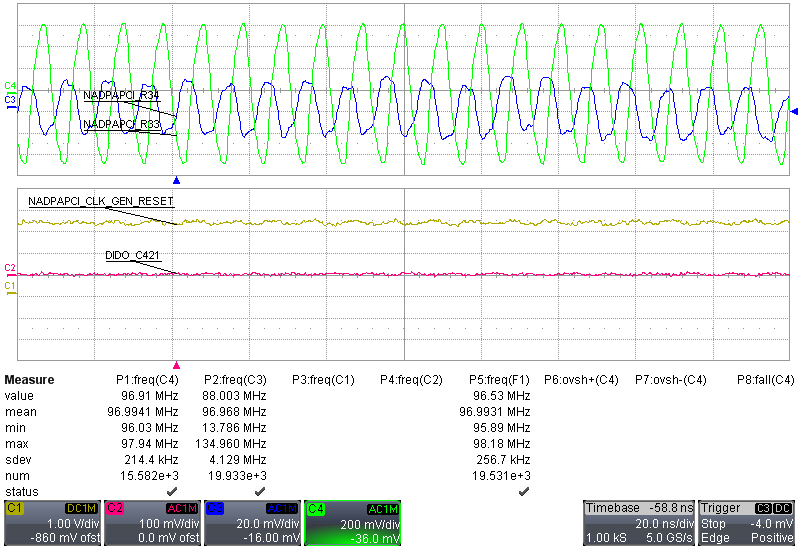

该模块使用20MHz 晶体振荡器计时、SERDES 信号使用提供100MHz 源的 CDCM61002RHBx 芯片计时。

您能帮助我们了解哪些因素会导致此问题吗?

谢谢

Umberto