工具/软件:Linux

您好 ,专家:

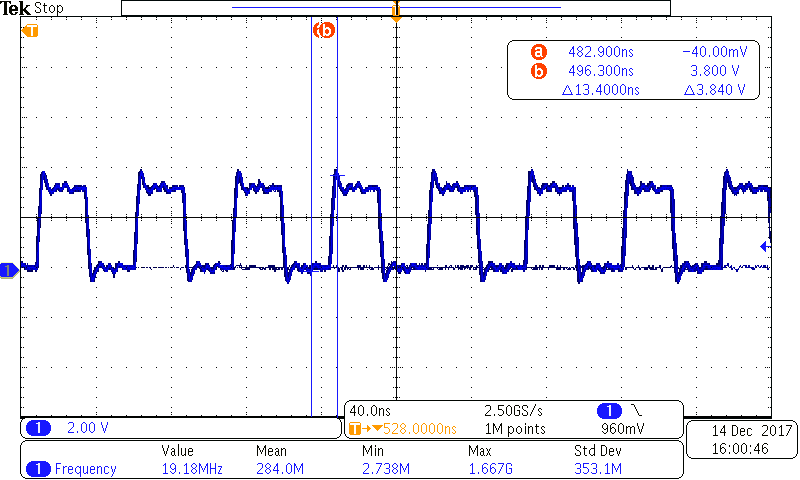

我们发现 visionsdk 2.12.02 Linux 以~19Mhz 的频率运行 QSPI 速度设置。

在 uboot 时、我们将 QSPI 速度设置为76.8MHz。 (arch/arm/dts/dra71-evm.dts)、探测 QSPI 时钟信号、速度为76.8MHz。

但是、当内核启动时、首先探测 QSPI 时钟、它是76.8MHz、当进入 Linux 控制台时、QSPI 读取/写入速度仅为19MHz。

默认模式读取0x4b000040、它是0x80000004。

使用 omapconf 写入0x4b300040 0x8000000001将 QSPI 时钟 div 从4更改为1。 在内核上、QSPI 速度变为76.8MHz。

请帮助我们检查代码中的哪个部分在内核上更改了 QSPI 速度?

在 DTS 文件中、我们将 QSPI 最大速度设置为76.8MHz、但我们没有更改哪个代码部分的 QSPI 时钟设置。

此致!

韩涛