尊敬的香榭丽舍

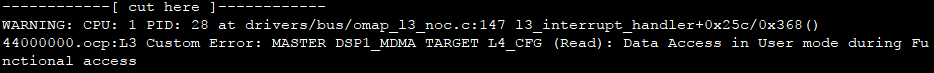

我的客户在 DSP 初始化 PCIe 时发现以下错误、您能否检查以下错误是什么以及如何解决该错误?

实际上、他们在尝试访问 DSP 中的 PCIe 时遇到了与 ARM 的冲突、并删除了 ARM Linux-RT 中与 PCIe 相关的所有内容、如下面的 e2e 中所述。 他们认为他们的问题已在 ARM Linux 中通过这些删除工作得到解决、但在尝试测试更多内容时、他们有时会发现上述错误。

其软件信息如下所示。

主机 PC 操作系统:Ubuntu 16.04 Linux 64位

AM5728 SDK:U-boot-2016.05 / Linux-RT-4.4.19

AM5728 SDK 版本:TI-processor-sdk-linux-rt-am57xx-evm-03.01.00.06

IPC:IPC_3_43_02_04

XDC:xdctools_3_32_00_06_core

谢谢、此致、

SI