尊敬的 TI 教授:

我将 Altera FPGA PCIe 通信与 c6678结合使用、FPGA 用作 EP、DSP 用作 RC.I wanner 意识到 FPGA 控制 AD 转换器可采集数据并将数据保存到 FIFO 中。 当 FIFO 满时、将触发中断向量为0的 MSI、DSP core0接收中断并远程配置 FPGA DMA 寄存器、以将数据从 FPGA FIFO 传输到 DSP DDR3 SDRAM。 当 DMA 触发 DMA 传输结束 MSI 中断向量为1时、DSP core0接收 msi 中断并通知 core1处理数据。

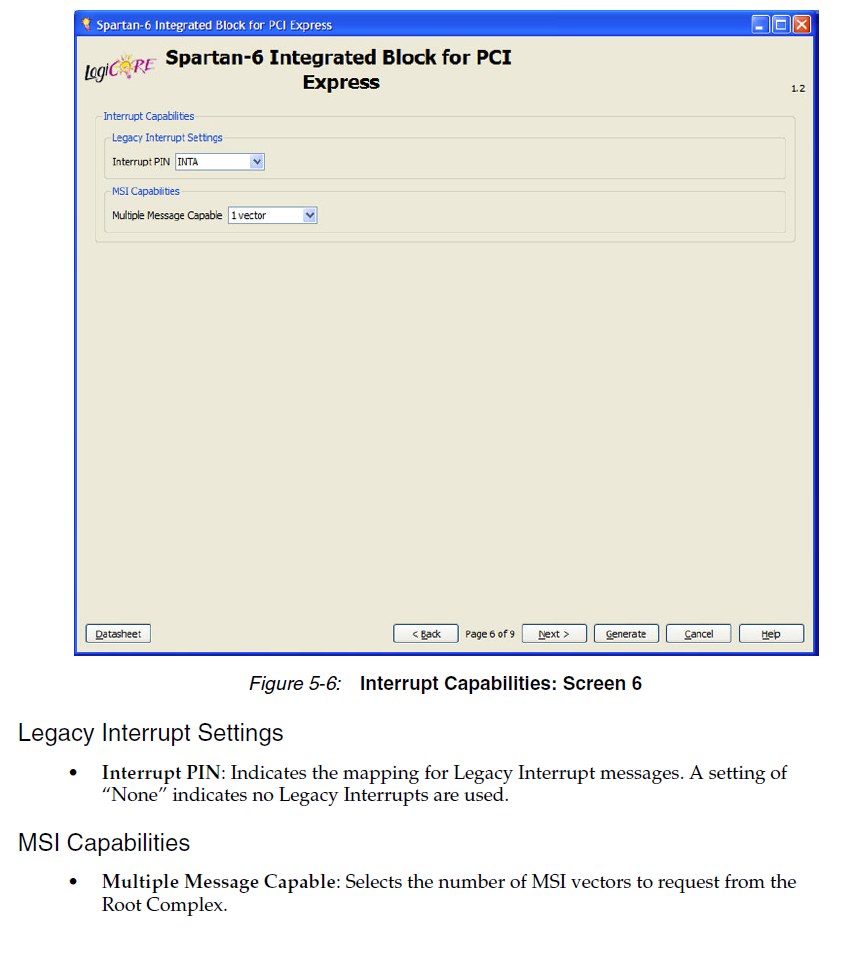

现在、我的问题是 FPGA 将触发两个 msi 中断、中断矢量是0和1、 core0接收两个 msi 中断 、但显示常见的中断矢量。我查看 PCIe 规范数据表、我发现 MSI 矢量必须继续、msi-x 中断矢量可以停止。但 DSP core0仅接收 msi 矢量是0、8、16和24。这意味着 FPGA 无法向发送两个 msi 中断 DSP。

我不确定我是否理解这一权利。 您能给我一点关于 DSP core0从 FPGA 接收两个 msi 的想法吗?

想一想!