Other Parts Discussed in Thread: LP8732-Q1, LP8733-Q1

主题中讨论的其他器件: LP8732-Q1、 LP8733-Q1

工具/软件:Linux

尊敬的:

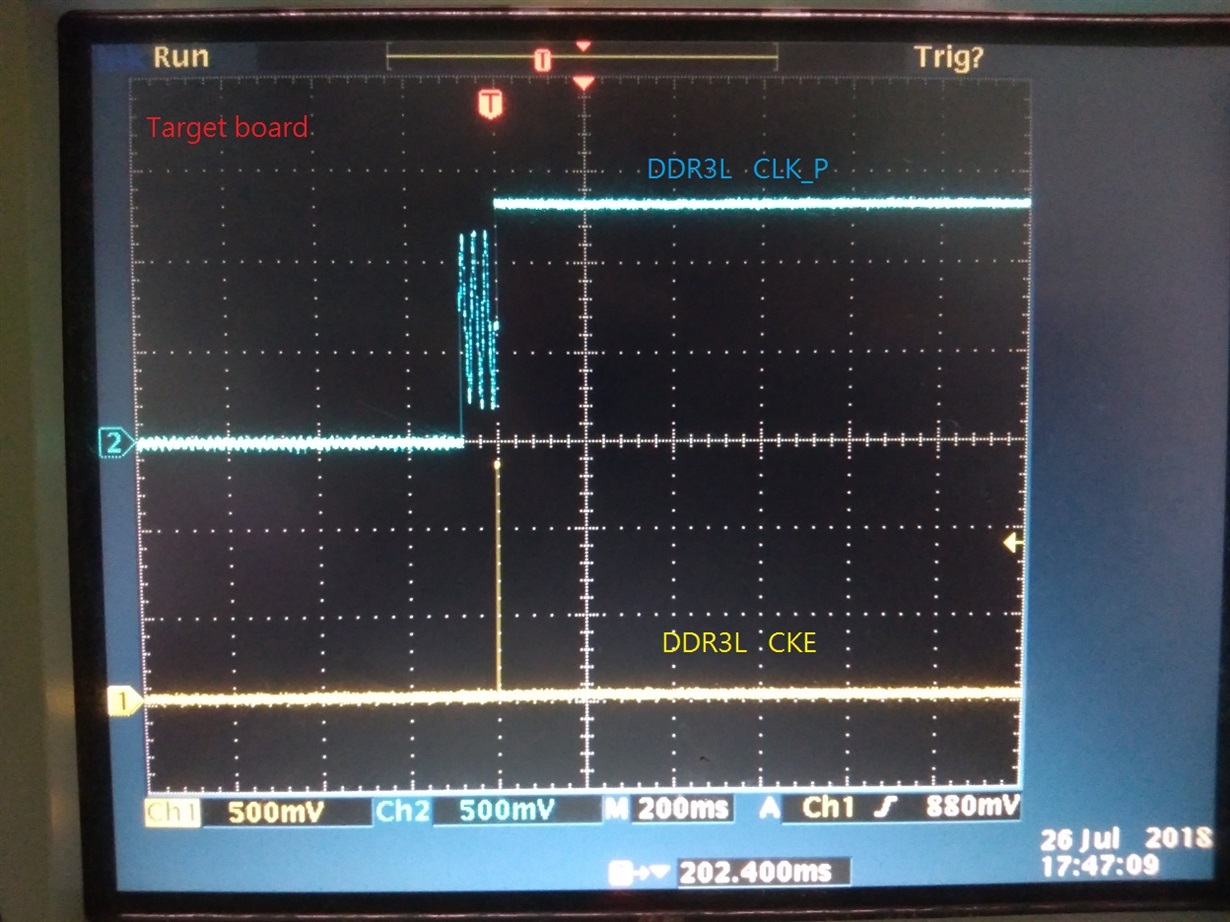

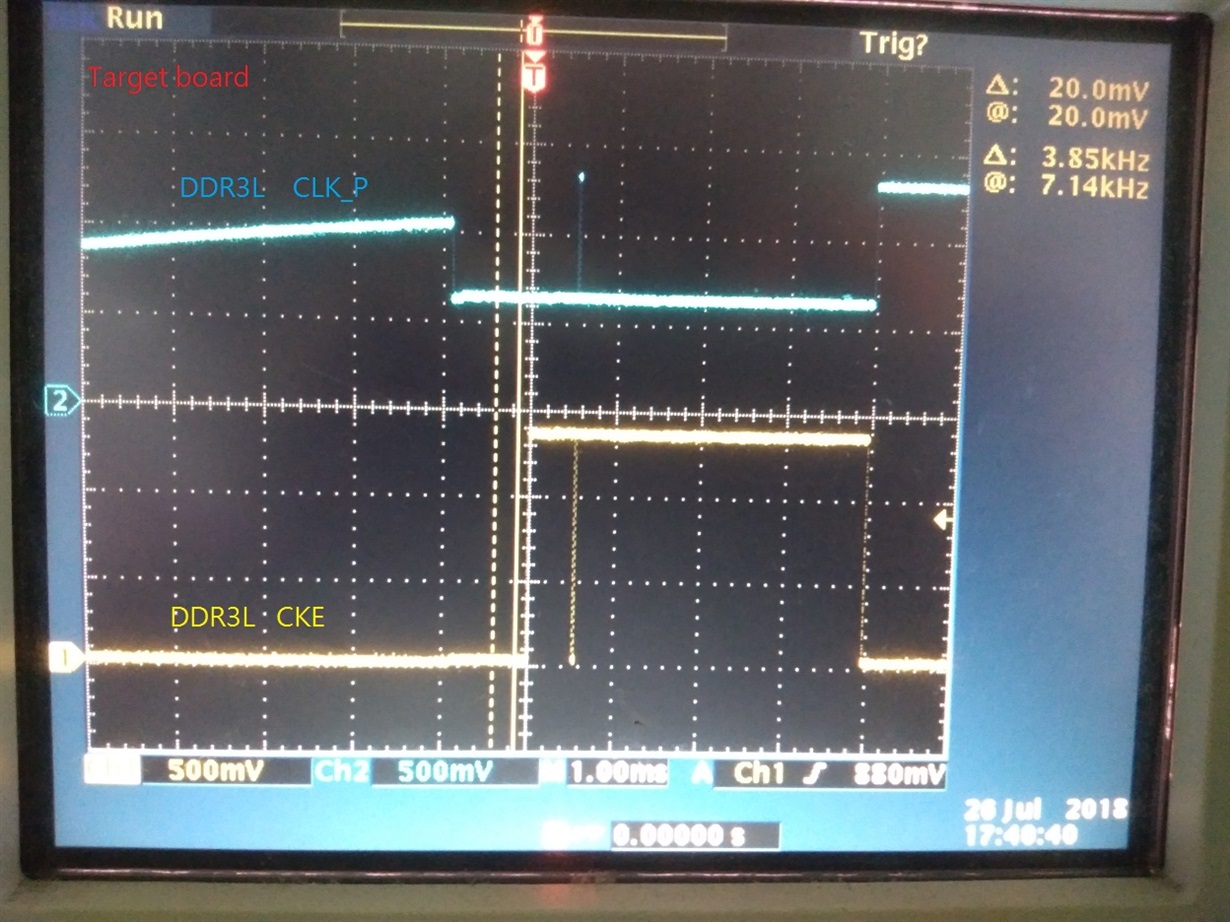

J6条目 DRA718 e2e.ti.com/.../1004.nu100_5F00_20180419_2D00_core_2D00_TI.pdfcan't从 SD 卡引导(QSPI 和 eMMC 都为空)、UART1 TX 上没有任何消息。

我的状态是

a.为 J6Entry 供电的 LP8733-Q1和 LP8732-Q1加电序列用户指南图2.

b. SD 卡中的引导加载程序(518202 J6入门级 EVM 板版本)。

c. Choice SYSBOOT[5:0]= 0b100010 => SD 引导。

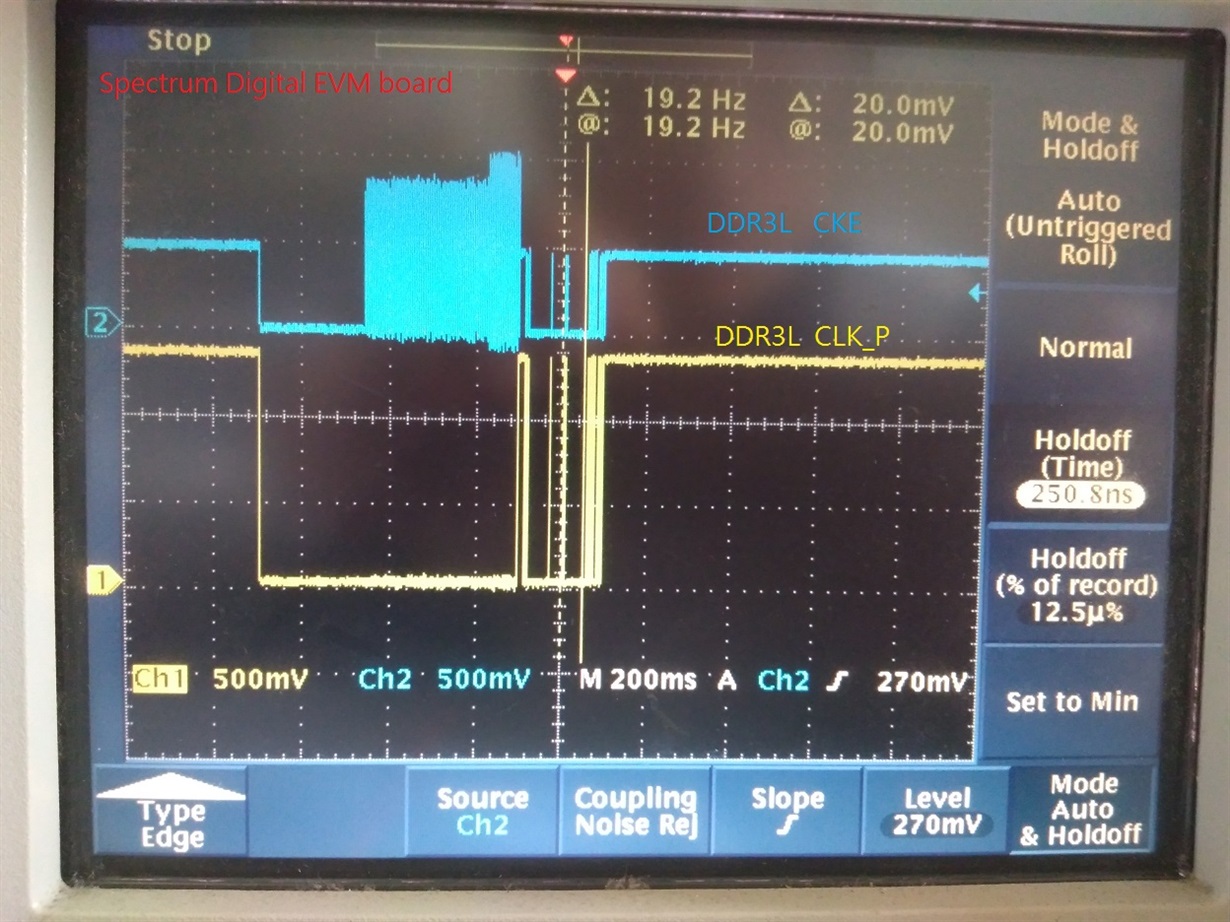

d.在 J6入口使用19.2MHz 晶体,sysboot[9:8]= 0b11 (19.2MHz 为518392 J6入口低 REF 版本)。

e.复位信号(PORz)为高电平。

我们尝试将引导加载程序更改为518392 J6低 REF 版本(从 Web 下载)、但 UART 上仍然没有任何消息。

(下载518392加载程序可能不正确。)

请问您该怎么办?

非常感谢。

Ryan。