成功连接多个 LCD 显示屏后、我遇到了一个特定接口的问题。 显示屏要求 HSync 和 VSync 同时下降。

我是否有任何方法可以配置芯片来实现这一目的? 我已经尝试了 Timing2寄存器的各种组合。 逻辑分析仪确认所有其他信号都正确。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

成功连接多个 LCD 显示屏后、我遇到了一个特定接口的问题。 显示屏要求 HSync 和 VSync 同时下降。

我是否有任何方法可以配置芯片来实现这一目的? 我已经尝试了 Timing2寄存器的各种组合。 逻辑分析仪确认所有其他信号都正确。

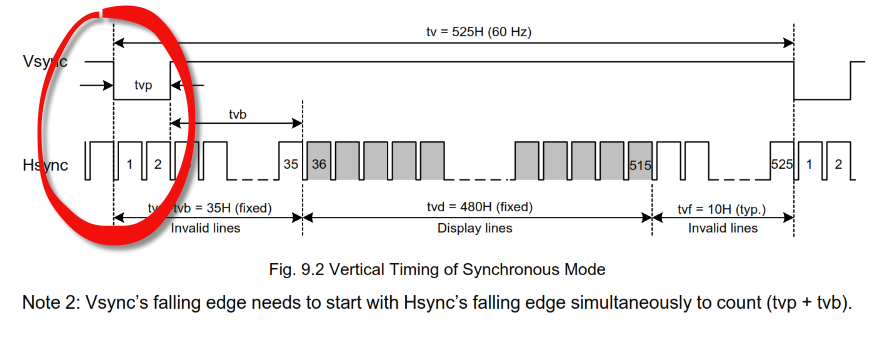

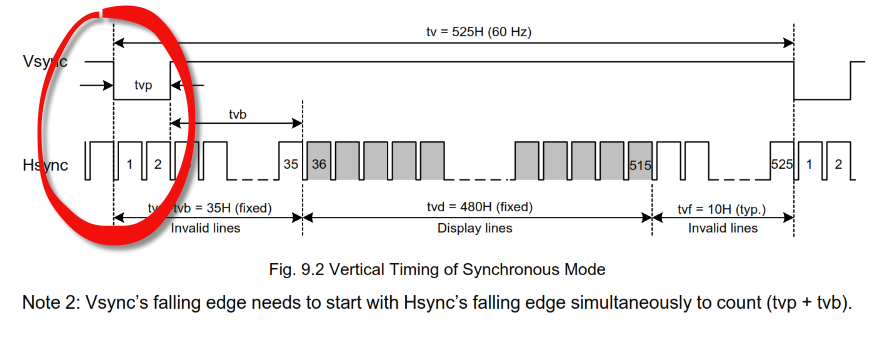

谢谢。 我一直在使用 Rev O。Rev P 在13-27中添加了时序图。

请注意、显示了 HSync 前沿的 VSync 变化。

我尝试了 RasterTiming2 PHSVS_RF 和 PHSVS_ON_OFF 的所有组合、并且 HSYNC 的后沿超前 VSync。 我在 IVS/IHS 中尝试过这种情况、除了反转、结果和设置都相同。

大画面看起来不错。 我已经验证了 HSW、HBP、HFP、VSW、VBP 和 Vfp 的时钟数量以及数据时钟。 下面的捕获显示了一直到 Vsync 的同步:

但从细节来看、很明显、我有 Hsync 领先的 Vsync

这与13-27中的描述不匹配。 如果我可以生成13-27、同时激活 Vsync 和 Hsync、我就满足 LCD 要求。

我看不到会影响同步相位的任何其他寄存器;

有什么建议吗? 还是 TRM 中的数字错误?