主题中讨论的其他器件: TMS320TCI6608

我们阅读了数据表并有疑问,尤其是关于信号 CORRECLKP、CORRECLKN、DDRCLKP、DDRCLKN、PCIECLKP、PCIECLKN 的测量标准

以 TMS320C6678为示例,附带数据表 《TMS320C6678SPRS691D - 2013年4月 多核定点和浮点数字信号处理器 SPRS691D - 2013年4月》

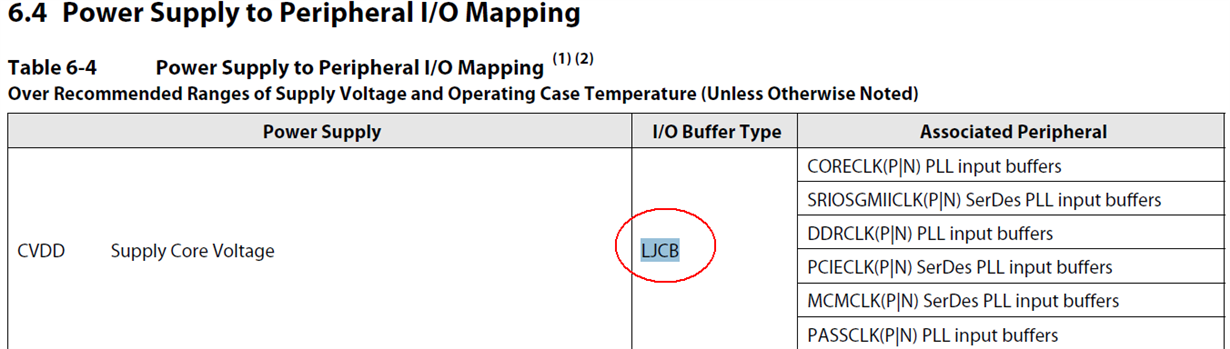

1、第116页、117,LVDS/LJCB 的 VIH/VIL/摆幅/共模电压 ?

输入电压(VI)范围:

所有差分时钟输入均符合 LVDS 电气规范 IEEE 1596.3-1996、所有 SERDES I/O 均符合 XAUI 电气规范 IEEE 802.3ae-2002。

2、 什么是 CORECLKP、CORECLKN、DDRCLKP、DDRCLKN、PCIECLKP、PCIECLKN?PCIECLKN 的 VIH/VIL/摆幅/共模电压

我们应注意差分信号或单端信号。? ?以及应测量信号的参数

我们期待 您早日回复!