您好!

AM625X 设计有以下问题:

1. 请告知最大值 GPMC 的运行速率;

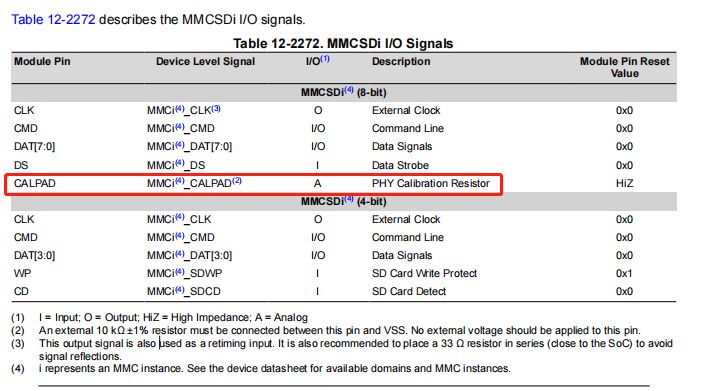

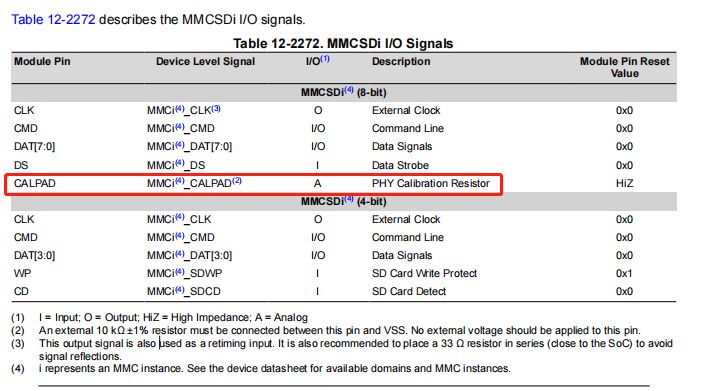

请为设计中的 PHY 校准电阻器提供位置、我们在设计中找不到该位置;

3.请告知 SOC 是否与 RGMI 与 SOC 通信;

4.请告知如何使用 LVDS 到2个通道,我们考虑使用 Lane1-2到 LVD#1,而 Lane3-4到 LVD#2。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

AM625X 设计有以下问题:

1. 请告知最大值 GPMC 的运行速率;

请为设计中的 PHY 校准电阻器提供位置、我们在设计中找不到该位置;

3.请告知 SOC 是否与 RGMI 与 SOC 通信;

4.请告知如何使用 LVDS 到2个通道,我们考虑使用 Lane1-2到 LVD#1,而 Lane3-4到 LVD#2。

您好张良

感谢您的查询。

我们建议在包含外设标题的单个查询中添加特定于子系统或外设的查询、以接触更广泛的受众。

您能否将主题帖标题编辑为 GPMC 频率。

下面是针对 GPMC 频率的回复。 和 MMC

[引用 userid="507183" URL"~/support/processors-group/processors/f/processors-forum/1193228/am625-am625x-design-issue ]1. 请告知最大值 GPMC 的运行速率;[/报价]1 μ A×用途存储器控制器(GPMC)

高达133 MHz

参考-数据表

[引用 userid="507183" URL"~/support/processors-group/processors/f/processors-forum/1193228/am625-am625x-design-issue "]请确定设计中 PHY 校准电阻器的位置,我们在设计中找不到该位置;[/quot]因为我了解 PHY 计算盘没有输出引脚。

参考-数据表

[引用 userid="507183" URL"~/support/processors-group/processors/f/processors-forum/1193228/am625-am625x-design-issue "]

3.请告知 SOC 是否与 RGMI 与 SOC 通信;

4.请告知如何使用 LVDS 到2个通道,我们考虑使用 Lane1-2到 LVD#1,而 Lane3-4到 LVD#2。

[/报价]

请为 RGMII 接口启动新主题。

对于 Q.4、请在新线程中详细说明与该查询相关的查询和外设。

此致、

Sreenivasa

您好张良

我在内部进行了检查、并更新了以下内容的信息。

[引用 userid="177086" URL"~/support/processors-group/processors/f/processors-forum/1193228/am625-am625x-design-issue/4497806 #4497806"]请确定设计中 PHY 校准电阻器的位置,我们在设计中找不到该位置;这仅适用于 AM64x 的 MMC0端口。 它不适用于 AM62x 的 MMC0端口和未来的 AM62X 器件。

TRM 是一个通用图、有关该引脚的可用性、请参阅数据表。

此致、

Sreenivasa