尊敬的 TI 团队:

我正在尝试同步 AM65x 作为 PCIe EP 运行、并通过 PCIe PTM 连接到 x86处理器。

在 PCIe 寄存器空间中启用 PTM 后、显然会同步 PTM 本地时钟、即 PTM_REQ_Context_VALID 寄存器已设置、我可以看到 PCIe_EP_PTM_REQ_LOCAL_LSB_OFF/...MSB_OFF 设置为与 x86的当前 PTM 时间匹配的值。

我的问题是、我尚未找到使用 PTM 本地时钟同步 AM65x 内其他时钟的可靠方法。 我看到的主要问题是 PTM 时钟更新与 CPTS 模块不同步。 如果 PTM 本地时钟未调整到 PTM 主器件的频率、则 PTM 本地时钟将从主器件时钟漂移。 这意味着我必须确保最近更新了 PTM 本地时钟、但对于 PTM 本地时钟的低位、判断触发 CPTS 硬件推送事件的 PTM 本地时钟时间是多少变得困难/不可能。 对于 PTM 本地时钟的较高阶位、判断硬件推送事件发生时 PTM 本地时钟的时间当然会更容易、但最后一次 PTM 更新可能是毫秒级的时间、并且时钟会漂移。

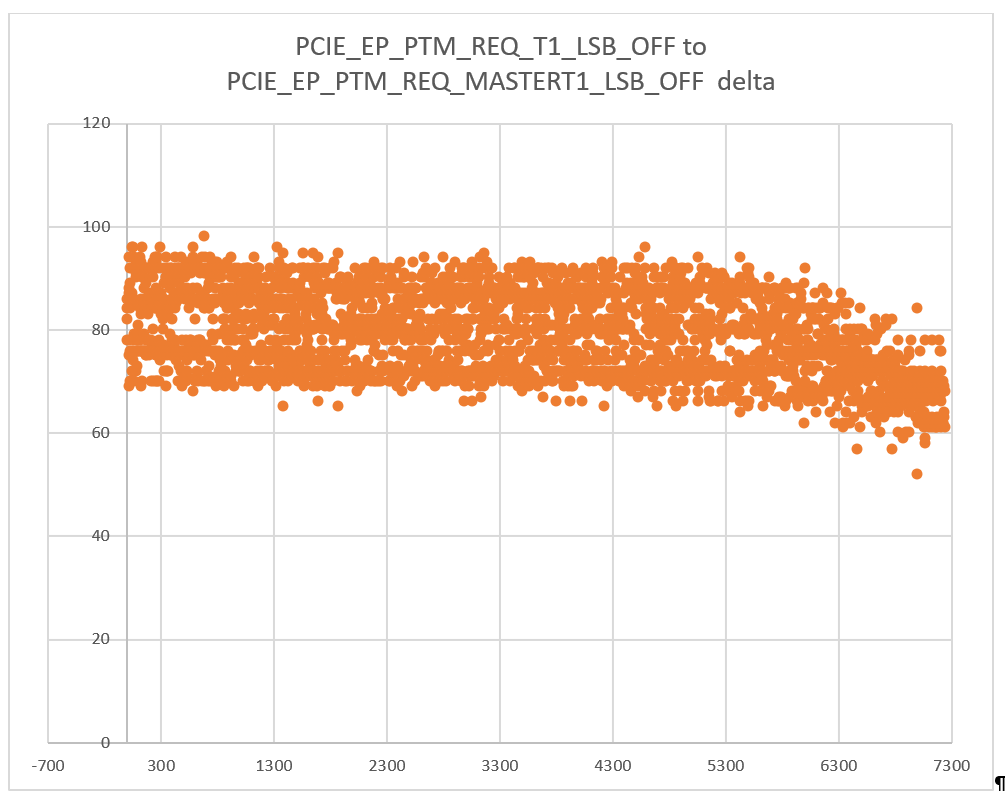

我假设 PTM 本地时钟的频率未调整为同步主时钟。 在我的当前测试中、我看到 PCIe_EP_PTM_REQ_T1_LSB_OFF 和 PCIe_EP_PTM_REQ_MASTERT1_LSB_OFF 寄存器中的成功上下文更新(PTM_CLK_Updated interrupts)之间存在~80ns 的差异。

- 是否可以安全地假设 PCIE_EP_PTM_REQ_T1与 PCIE_EP_PTM_REQ_MASTERT1在 PTM 请求者发起上次更新时显示了 PTM 本地时钟和 PTM 主时钟之间的差异?

- 在 PTM_CLK_updated 时钟信号发出之前、是否可以安全地假设 PTM 本地时钟已步进以匹配 PTM 主时钟?

- 我的假设是否正确、即 PTM 本地时钟未调整频率以匹配主时钟?

- 哪个时钟信号用于驱动 PTM 本地时钟?

我们非常感谢您提供有关如何使用 PCIe PTM/CPTS 功能的任何指导。

此致、

Dominic