您好、专家、

这是为了确认 DRA750 I2C3的行为(它与 DRA750相关:I2C3行为以及如何从 I2C 问题中恢复)

客户正在 I2C3上使用快速模式。

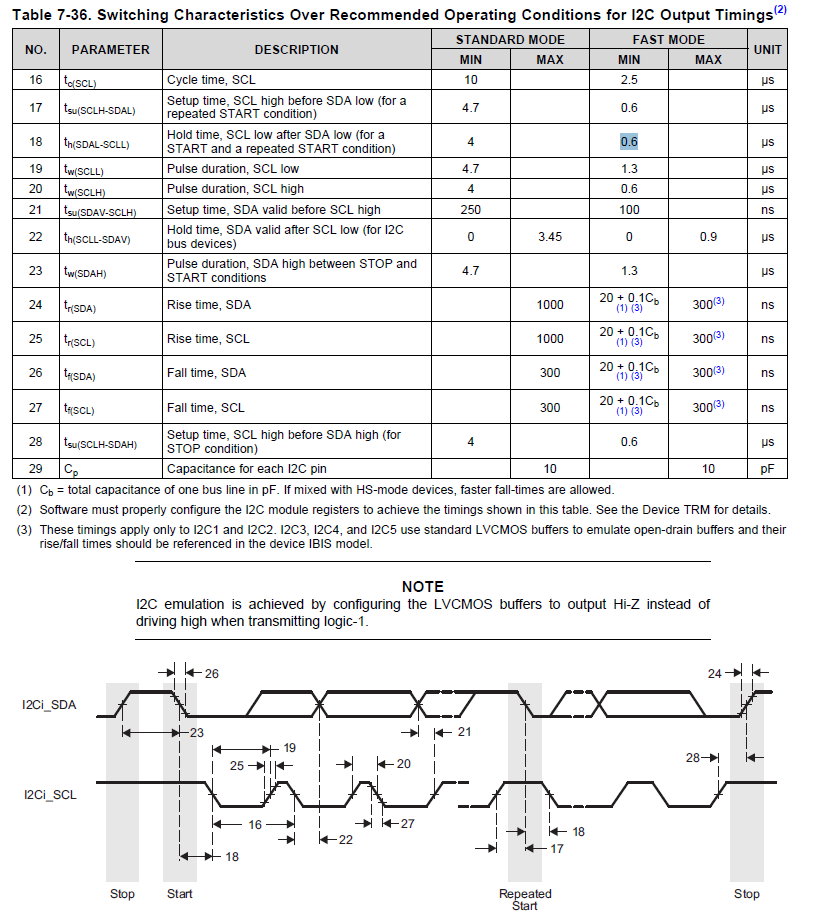

根据上面的 DRA75x 数据手册表7-36、TH (SDAL-SCLL)-保持时间 SCL 在 SDA 低电平之后(对于一个启动和一个重复启动条件)需要0.6uec 或更长时间才能进入启动条件。

[问题]换句话说、如果 Jacinto-6接收 SDA/SCL 时的 TH (SDAL-SCLL) wihich 始终小于0.6usec、Jacinto6 I2C3模块将永远不会识别为启动条件。 是这样吗?

连接到 Jacinto6 I2C3的外部 I2C 从器件(称为 CP)使 SCL 和 SDA 引脚在启动后非法变为低电平。

客户提到、CP SCL 和 SDA 输出时序会使 TH (SDAL-SCLL)小于0.6us。 因此、客户希望确认 Jacitno6 I2C3是否从未进入启动状态。

此致、

Saito