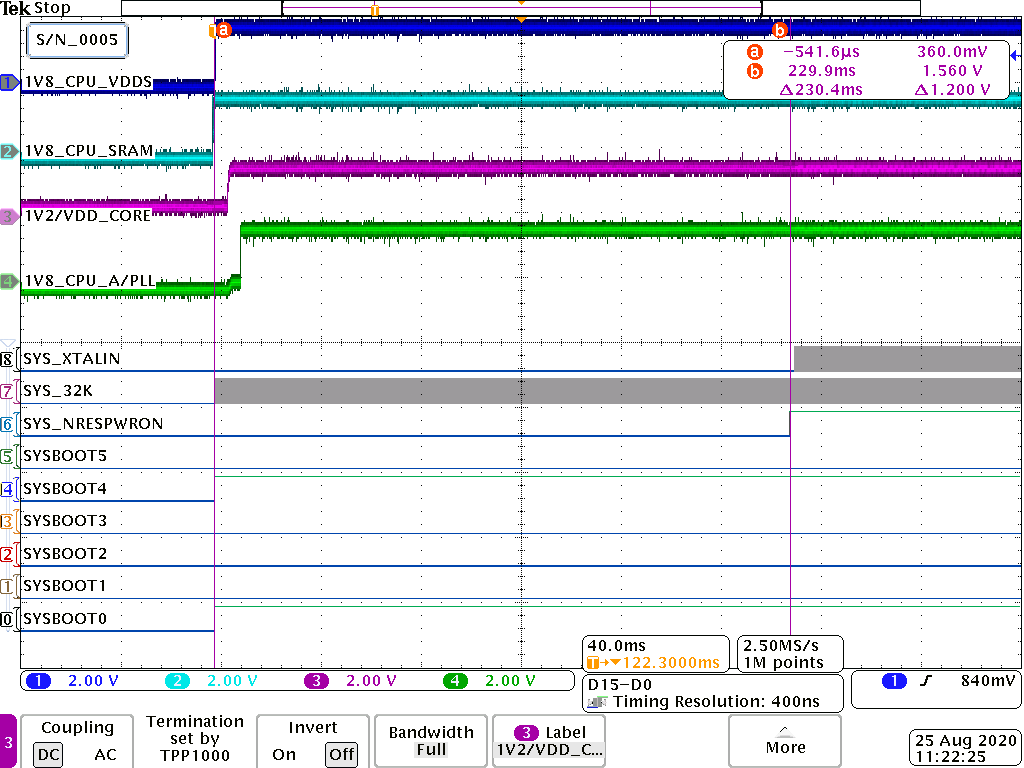

背景。 -我们正在新的原型 PCB 上运行 AM3505AZCN。 该设计与之前的设计非常相同、只需进行极少的更改。

问题-要从 UART3引导、我们将 SYSBOOT5 ("引导模式")置为逻辑1、然后脉冲 SYS_NRESPWRON "PwR_ON_RESET_N)。

在复位(SYSBOOT 5仍为 logic1)发布时、我们可以看到 UART3上的数据突发很小-仅为大约3字节。 在我们之前的设计中、我们看到大约60-70字节的大突发。

ASCI ID 似乎开始传输、然后中止?

我们已经验证的内容是正确的:

- 电源上电顺序(虽然最初不正确-现在已修复)

- 26MHz 时钟

- 32kHz 时钟

- SYS_NRESPWRON

- 当我们将位5置为逻辑1时、SYSBOOT (8:0)= 001110101

ASIC ID 传输为何会"中止"?

请告知我们接下来应该检查的其他内容。

提前感谢。