大家好、

以下是客户可能需要您帮助的几个问题:

1)

/cfs-file/__key/communityserver-discussions-components-files/140/zhca575.pdf

/cfs-file/__key/communityserver-discussions-components-files/140/sprugh7.pdf

从上述文档中可以看出、外部存储器的读取和写入方式可能有所不同、具体取决于 L2Cache 是否已打开以及其大小是否已打开。 打开 L2Cache 时、从 L2到外部 RAM 的速度较慢、从外部 RAM 到 L2的速度较快。 速度差异的主要原因是什么?

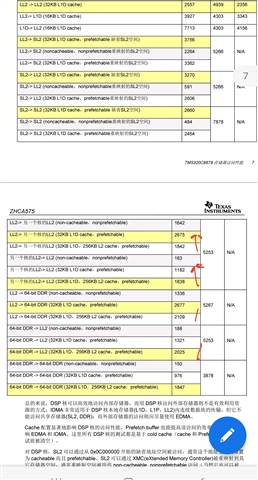

从 zhca575 doc 的表3中,CPU 访问内存:LL2<-->其它 CoreL2,LL2<--> DDR3。 下表显示当 CPU 内核访问内存 L2->>外部存储时、启用 L2缓存传输时速度会降低。

| 传输 | 32KBL1D,可预取 | 256KB L2、32KB L1D、可预取 |

| L2->OtherLL2 | 2675 | 1842. |

| 其他 L2->LL2 | 1182. | 1838. |

| L2->DDR3 | 2677 | 2109. |

| DDR3->LL2 | 1321. | 2025年 |

2) 2) 根据 zhca575 doc、从图2、图4中可以明显看出、STDW 访问存储器的延迟比 LDDW 小、LDDW 不应与高速缓存相关。

根据 sprogh7 doc 中的 LDW、STW 和其他相关指令、类似 LDW 的指令必须经过多个周期才能将存储器的内容移动到内部寄存器。 此 c66x 设计的原因是什么? 如果 LDW 的内存为 L1RAM、1个周期应该能够完成数据移动。

3) 3) 每个内核的 L2可通过在 zhaca575文档中测试的全局地址进行读取和写入。 未引导内核可用作引导内核外部 RAM、其访问性能低于 SL2。

如果程序中的高速缓存大小是动态调整的、那么最初在 RAM 或高速缓存中分配的数据是否会丢失?

例如、在以下情况下:

a:全局变量 x 在 L2分配、程序在 L2缓存大小调整后运行、全局变量 x 的地址在缓存调整范围内。 当变量 x 遇到缓存 inv、缓存 wb 等时会发生什么情况?

b.在平台中、将 lL2缓存大小配置为32K、将剩余的 L2配置为数据存储器、并在程序运行时将 L2缓存大小调整为0K。 局部变量是否会放置在 L2为空的 RAM 中? 空 RAM 能否仅动态用作 Heapmem、HeapBuf 等?

您可以帮助检查此案例吗? 谢谢。

此致、

樱桃