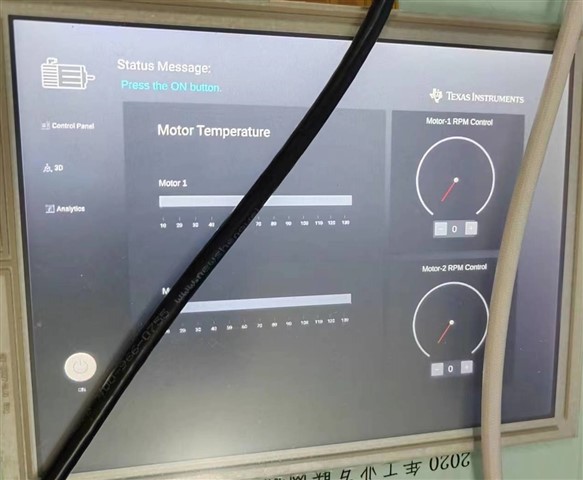

在客户电路板上、不存在 OLDI0_CLK0输出。 但数据引脚具有输出。 测试3块电路板、结果相同、PSDK8.04。

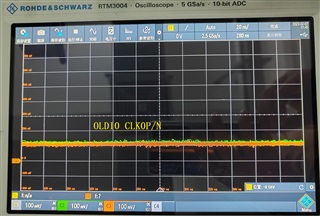

连接面板 OLDI0_CLK0时、如下所示、仅为100mV。

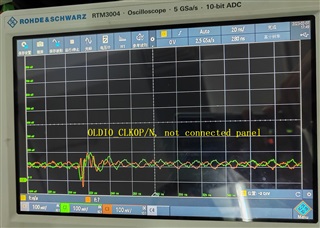

未连接面板时 、OLDI0_CLK0上会出现一些噪声。

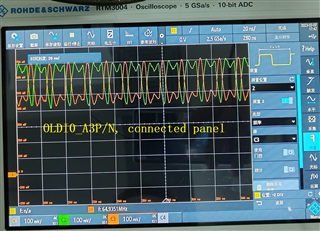

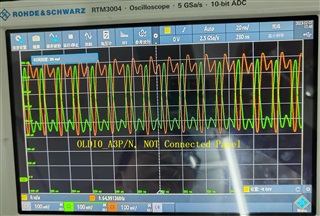

OLDI0_A3P/N 上

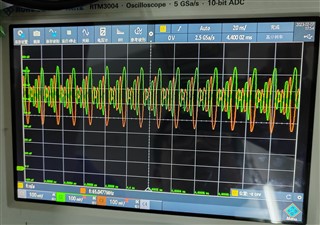

在 OLDI0_A0P/N 上、信号不如 OLDI0_A3P/N 好、

dts 文件

e2e.ti.com/.../k3_2D00_am625_2D00_sk_2D00_GSK_2D00_chenjianfei.dts

kmsproint

软件配置是否存在硬件问题? 硬件连接非常简单、只是点对点连接。 请建议如何识别?