主题中讨论的其他器件:SK-AM62

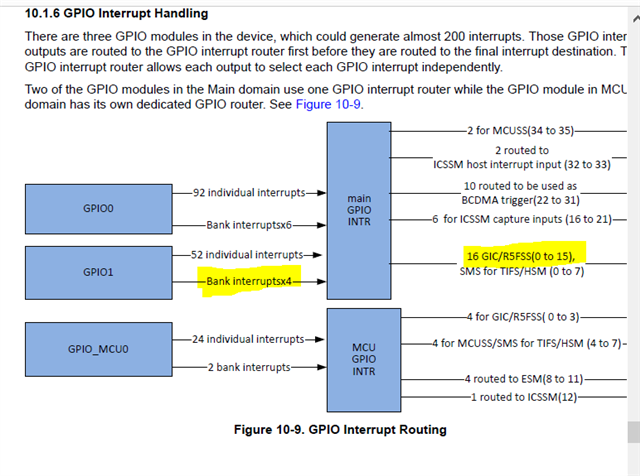

我正在尝试一个使用基于 GPIO 的中断的设计。 我们希望利用 GPIO1_44-47作为中断。 我提到了两个具体例子,但似乎都不起作用。

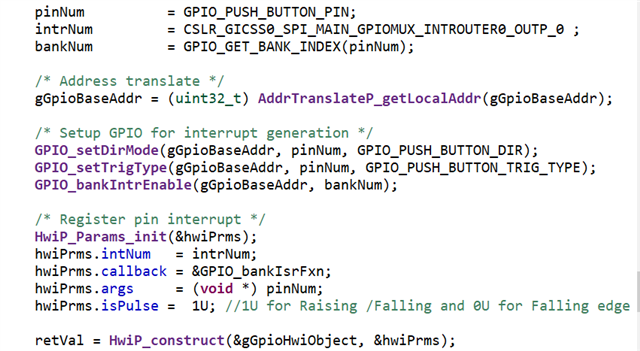

我尝试的第一个示例位于 Processor SDK QNX 08_05_00_0中。 具体而言、它是 psdkqa\QNX\examples\GPIO 示例。 当我尝试将其移植到我们的设计时、我能够成功构建、但第一次尝试写入 GPIO_MUX_BASE_PHY_ADDR 寄存器位置会导致"未处理异常"错误、导致单元崩溃。

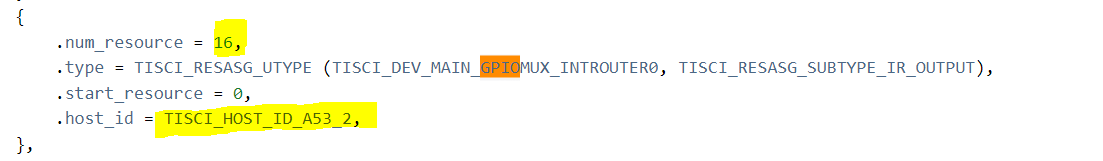

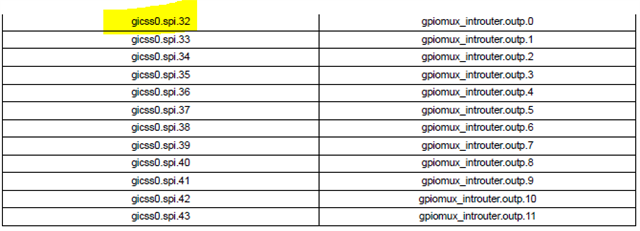

在进行一些 E2E 研究后、我们似乎需要使用 SCI 来配置中断路由器、但不清楚为什么这不是 SDK 使用的方法。 基于 https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1176076/processor-sdk-am62x-gic-interrupts/4469253?tisearch=e2e-sitesearch&keymatch=gpio%25252525252520%25252525252526%25252525252526%25252525252520interrupt#4469253

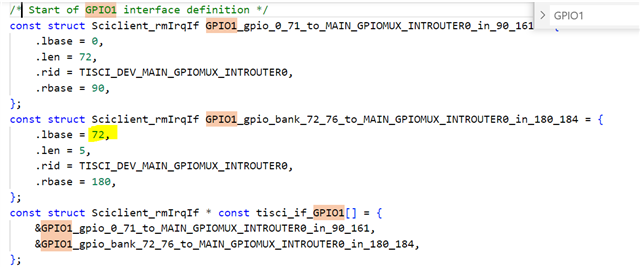

我们实施了以下代码、我认为这些代码应该配置中断路由器:

static void Sciclient_gpioIrqSet(void)

{

int32_t retVal;

struct tisci_msg_rm_irq_set_req rmIrqReq;

struct tisci_msg_rm_irq_set_resp rmIrqResp;

rmIrqReq.valid_params = 0U;

rmIrqReq.valid_params |= TISCI_MSG_VALUE_RM_DST_ID_VALID;

rmIrqReq.valid_params |= TISCI_MSG_VALUE_RM_DST_HOST_IRQ_VALID;

rmIrqReq.global_event = 0U;

rmIrqReq.src_id = TISCI_DEV_MAIN_GPIOMUX_INTROUTER0; //MCU_GPIO_MUX_INT_ROUTER_ID;

rmIrqReq.src_index = 134U;//SRC_IDX_BASE_MCU_GPIO_BANK_0;

rmIrqReq.dst_id = TISCI_DEV_MAIN_GPIOMUX_INTROUTER0; //MCU_GPIO_MUX_INT_ROUTER_ID; // TISCI_DEV_MAIN_GPIOMUX_INTROUTER0 ?

rmIrqReq.dst_host_irq = 32U; //MCU_GPIOMUX_INTROUTER_MCU_0_OUTP_6;

rmIrqReq.ia_id = 0U;

rmIrqReq.vint = 0U;

rmIrqReq.vint_status_bit_index = 0U;

rmIrqReq.secondary_host = TISCI_MSG_VALUE_RM_UNUSED_SECONDARY_HOST;

retVal = Sciclient_rmIrqSetRaw(&rmIrqReq, &rmIrqResp, -1);

if(0 != retVal)

{

cout << "[Error] Sciclient event config failed!!! RetVal=" << retVal << endl;

//DebugP_log("[Error] Sciclient event config failed!!!\r\n");

//DebugP_assert(FALSE);

}

return;

}

使用此代码会导致错误消息: [ERROR] Sciclient 事件配置失败!!! RetVal=-1。 对 slog 的进一步探讨表明、每次执行函数都会导致 slog 中出现一个新条目: Jan 05 18:52:59.587 tisci_mgr.323598 slog 55

TI_sci_msg_xfer (252):ACK 上的 sciclient 服务调用失败

是否有人可以指引我查看适用于 AM62x 设计的示例?

谢谢、

John