主题中讨论的其他器件:TDA4VH

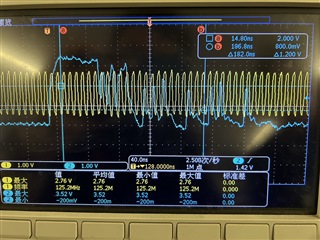

两个 TDA4VH 芯片通过主域的 RGMII 接口将 MAC 连接到 MAC;千兆位通信调试失败;示波器测量显示 TX 数据信号 无法达到芯片的 电平阈值; 如下图所示、数据01后跟11、导致提升的电平为0。 同样、10后跟00、导致1个电平下拉。 我觉得数据驱动能力太差; 如果有可被配置和修改以提高数据信号驱动能力的寄存器、您能帮我吗? 此外、为什么时钟信号的长度相同?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Chen、

时钟和数据具有相同的驱动强度。 不过、clk 始终在切换。 不断切换时、它可能无法达到满量程电压(Vcc/GND)。而 TX 由于重复的位(00或11)、它将有足够的时间下降到 GND 或 Vcc 电平。 然后、当另一位转换时、它将没有足够的时间到达电源轨(Vcc 或 GND)。

似乎值得根据 TX/RX_CLK 通道的 PCB 布线长度来进行 IBIS 仿真。 布线长度可能足够长/有损耗、从而可能无法支持所需的上升/下降时间。

请参阅常见问题解答、查看 RGMII 的驱动强度控制。

100M 模式速度还行。IBIS 建模和仿真正在进行中。随附文档是 RGMII 信号部分的 PCB 图,您能否帮助检查 PCB 设计是否有任何问题?

两个器件附近的直列式电阻器是多少? 不应使用串联端接、因为 IO 输出阻抗设置为匹配50 Ω。 电路板阻抗是否受控/设置为50欧姆?

另一个建议是在同一层上对 TX 信号进行布线-这有助于匹配接口上的偏差。 不同过孔数量和不同层上的布线会导致信号传播延迟不同。 (RX 信号具有类似注释)。

对于示波器捕获、探头位于何处? 请使用具有极短 GND 连接的高速验证来获取准确的图像。

如前所述、布线长度可能足够长/有损耗、从而可能无法支持所需的上升/下降时间。

串联电阻为0欧姆、PCB 布线阻抗约为45欧姆。

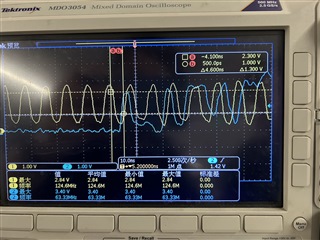

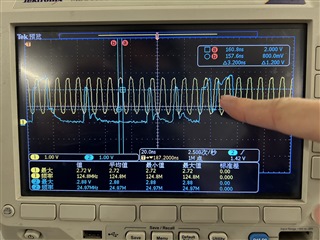

现在有一个问题。 通过 IBIS 仿真模型、提取 PCB 板的 S 参数进行仿真分析、仿真结果并不是很差、可以达到信号的高低阈值、但用高速示波器测出的信号却非常差 (探针的测试位置在芯片接收端的过孔处、GND 很短);目前看来 IBIS 仿真模型与实际测试不一致。

断开负载并测量芯片发送源处的 TXCLK 信号。 发现时钟波形上升沿的斜率很慢、是芯片本身缺乏驱动能力吗?