环境:

用于 uart1 RX 的 TMS320C6745 EDMA3

你能帮我吗?"

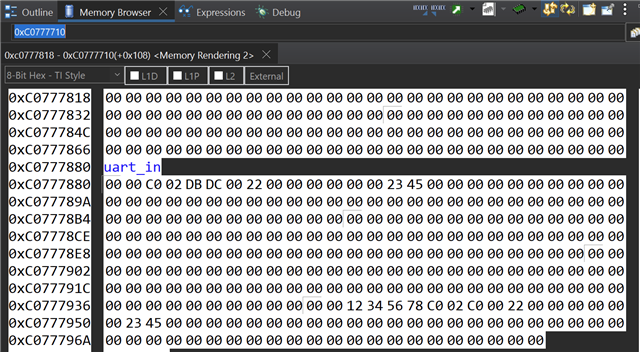

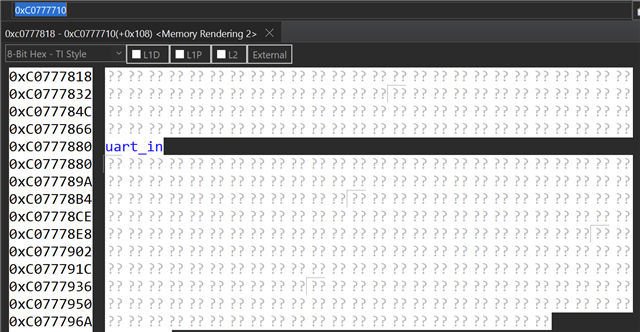

我将尝试查看 CCS12中的高速缓存存储器:

标记 L1D、L1P 和 L2字段的区别是什么? 在上面的视图中、我可以在停止调试器时看到内容。

如果我运行我看到的调试器、

当我标记 L1D 和 L2时、我只能看到00个字段。

原因是我为 uart1对 EDMA3进行了编程、而且我希望每次在 UART 中得到新数据时、我都会看到它

"Immediate"按钮。 这是可行的吗?

我的存储器控制器逻辑电路有问题吗、

#define cache_dma_NULL 0x00000000

#define cache_dma_L2WB 0x00000001

#define cache_dma_L2WBINV 0x00000002

#define cache_DMA_L2INV 0x00000004

#define cache_DMA_L2WWC 0x00000010

#define cache_DMA_L2WIWC 0x00000020

#define cache_dma_L2IWC 0x00000040

我仅使用 L2WC。 在哪里可以找到有关如何使用 DMA 编程的说明?

我将文件 SPRUFK5A 大型模块去掉、但对我来说不清楚。 您有 EDMA3 UART 示例吗?

此致

马丁