https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1248807/tmdxidk5718-am5718

器件型号:TMDXIDK5718您好!

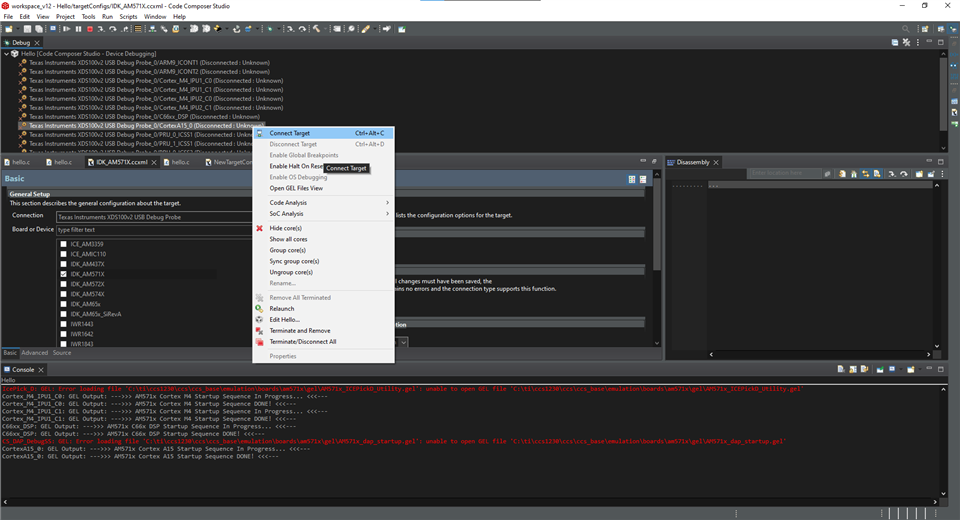

我正在尝试在 CCS 中运行 Hello World、但收到此错误。

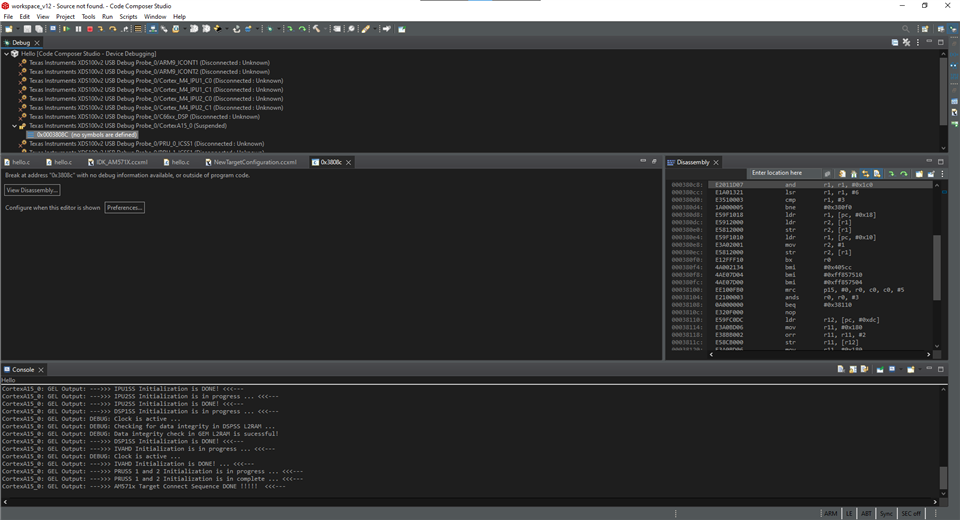

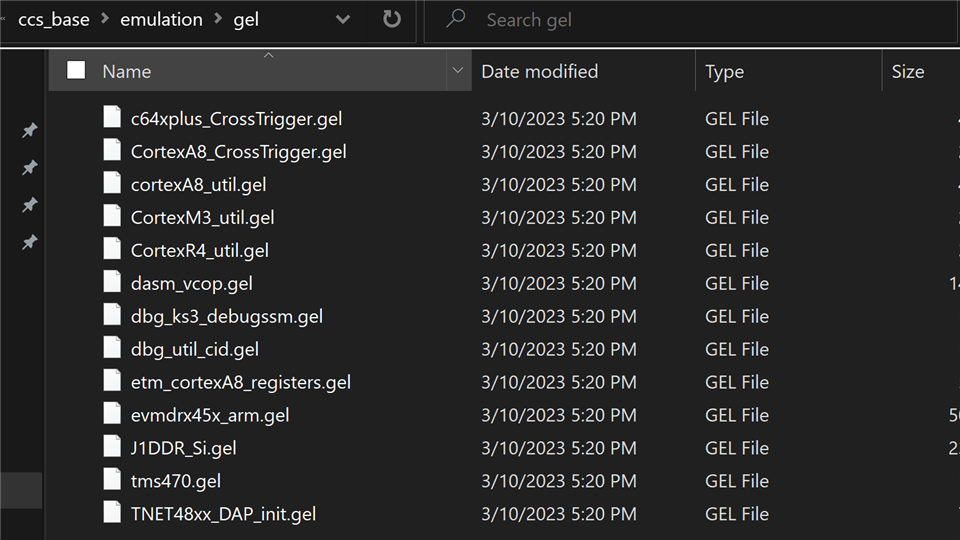

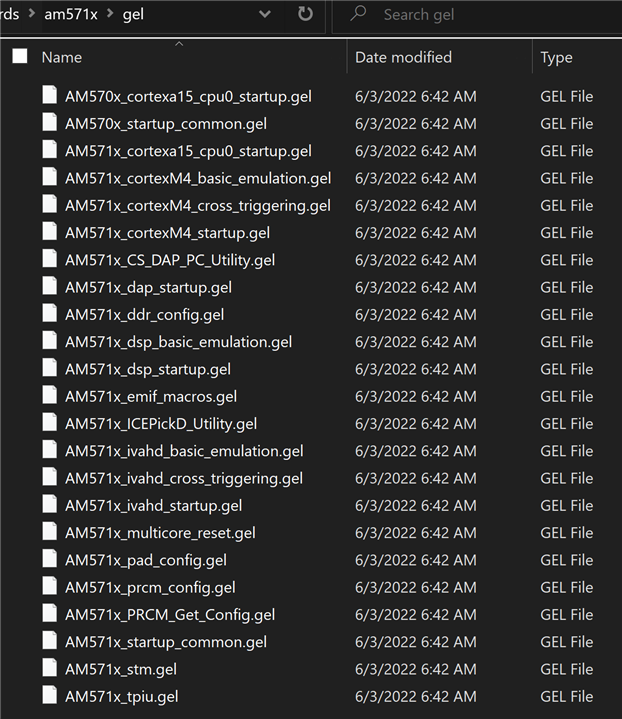

Cortex_M4_IPU1_C0: GEL Output: --->>> AM571x Cortex M4 Startup Sequence In Progress... <<<--- Cortex_M4_IPU1_C0: GEL Output: --->>> AM571x Cortex M4 Startup Sequence DONE! <<<--- Cortex_M4_IPU1_C1: GEL Output: --->>> AM571x Cortex M4 Startup Sequence In Progress... <<<--- Cortex_M4_IPU1_C1: GEL Output: --->>> AM571x Cortex M4 Startup Sequence DONE! <<<--- C66xx_DSP: GEL Output: --->>> AM571x C66x DSP Startup Sequence In Progress... <<<--- C66xx_DSP: GEL Output: --->>> AM571x C66x DSP Startup Sequence DONE! <<<--- CortexA15_0: GEL Output: --->>> AM571x Cortex A15 Startup Sequence In Progress... <<<--- CortexA15_0: GEL Output: --->>> AM571x Cortex A15 Startup Sequence DONE! <<<--- IcePick_D: GEL Output: Ipu RTOS is released from Wait-In-Reset. IcePick_D: GEL Output: Ipu SIMCOP is released from Wait-In-Reset. IcePick_D: GEL Output: IVAHD C66 is released from Wait-In-Reset. IcePick_D: GEL Output: IVAHD ICONT1 is released from Wait-In-Reset. IcePick_D: GEL Output: IVAHD ICONT2 is released from Wait-In-Reset. CS_DAP_DebugSS: GEL Output: --->>> CONFIGURE DEBUG DPLL settings to 1.9 GHZs <<<--- CS_DAP_DebugSS: GEL Output: > Setup DebugSS 1.9GHz in progress... CS_DAP_DebugSS: GEL Output: < Done with Setup DebugSS Trace export clock (TPIU) to 97MHz CS_DAP_DebugSS: GEL Output: < Done with Setup DebugSS PLL Clocking 1.9GHz CS_DAP_DebugSS: GEL Output: < Done with Setup DebugSS ATB Clocking 380MHz CS_DAP_DebugSS: GEL Output: < Done with Setup DebugSS Trace export clock (TPIU) to 97MHz CS_DAP_DebugSS: GEL Output: --->>> TURNING ON L3_INSTR and L3_3 clocks required for debug instrumention <<<<<<---- CS_DAP_DebugSS: GEL Output: ---<<< L3 instrumentation clocks are enabled >>>> --- CS_DAP_DebugSS: GEL Output: --->>> Mapping TIMER supsend sources to default cores <<<<<<---- CS_DAP_PC: GEL Output: Cortex-A15 1 is not in WIR mode so nothing to do. CortexA15_0: GEL Output: --->>> AM571x Target Connect Sequence Begins ... <<<--- CortexA15_0: GEL Output: --->>> AM571x PG2.0 GP device <<<--- CortexA15_0: GEL Output: --->>> PRCM Clock Configuration for OPPNOM in progress... <<<--- CortexA15_0: GEL Output: Cortex A15 DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: Cortex A15 DPLL is already locked, now unlocking... CortexA15_0: GEL Output: Cortex A15 DPLL OPP 0 is DONE! CortexA15_0: GEL Output: IVA DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: IVA DPLL OPP 0 is DONE! CortexA15_0: GEL Output: PER DPLL OPP 0 clock config in progress... CortexA15_0: GEL Output: PER DPLL already locked, now unlocking CortexA15_0: GEL Output: PER DPLL OPP 0 is DONE! CortexA15_0: GEL Output: CORE DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: CORE DPLL OPP already locked, now unlocking.... CortexA15_0: GEL Output: CORE DPLL OPP 0 is DONE! CortexA15_0: GEL Output: ABE DPLL OPP 0 clock config in progress... CortexA15_0: GEL Output: ABE DPLL OPP 0 is DONE! CortexA15_0: GEL Output: GMAC DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: GMAC DPLL OPP 0 is DONE! CortexA15_0: GEL Output: GPU DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: GPU DPLL OPP 0 is DONE! CortexA15_0: GEL Output: DSP DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: DSP DPLL OPP 0 is DONE! CortexA15_0: GEL Output: PCIE_REF DPLL OPP 0 clock config is in progress... CortexA15_0: GEL Output: PCIE_REF DPLL OPP 0 is DONE! CortexA15_0: GEL Output: --->>> PRCM Clock Configuration for OPP 0 is DONE! <<<--- CortexA15_0: GEL Output: --->>> PRCM Configuration for all modules in progress... <<<--- CortexA15_0: GEL Output: --->>> PRCM Configuration for all modules is DONE! <<<--- CortexA15_0: GEL Output: --->>> DDR3 Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DDR DPLL clock config for 666MHz is in progress... CortexA15_0: GEL Output: DDR DPLL clock config for 666MHz is in DONE! CortexA15_0: GEL Output: Launch full leveling CortexA15_0: GEL Output: Updating slave ratios in PHY_STATUSx registers CortexA15_0: GEL Output: as per HW leveling output CortexA15_0: GEL Output: HW leveling is now disabled. Using slave ratios from CortexA15_0: GEL Output: PHY_STATUSx registers CortexA15_0: GEL Output: --->>> DDR3 Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> Mapping TIMER supsend sources to default cores <<<<<<---- CortexA15_0: GEL Output: --->>> IPU1SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: --->>> IPU1SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> IPU2SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: --->>> IPU2SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> DSP1SS Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DEBUG: Clock is active ... CortexA15_0: GEL Output: DEBUG: Checking for data integrity in DSPSS L2RAM ... CortexA15_0: GEL Output: DEBUG: Data integrity check in GEM L2RAM is sucessful! CortexA15_0: GEL Output: --->>> DSP1SS Initialization is DONE! <<<--- CortexA15_0: GEL Output: --->>> IVAHD Initialization is in progress ... <<<--- CortexA15_0: GEL Output: DEBUG: Clock is active ... CortexA15_0: GEL Output: --->>> IVAHD Initialization is DONE! ... <<<--- CortexA15_0: GEL Output: --->>> PRUSS 1 and 2 Initialization is in progress ... <<<--- CortexA15_0: GEL Output: --->>> PRUSS 1 and 2 Initialization is in complete ... <<<--- CortexA15_0: GEL Output: --->>> AM571x Target Connect Sequence DONE !!!!! <<<--- CortexA15_0: File Loader: Verification failed: Values at address 0x00000020 do not match Please verify target memory and memory map. CortexA15_0: GEL: File: C:\Users\223106495\Hello\Hola\Debug\Hola.out: a data verification error occurred, file load failed. CortexA15_0: Unable to terminate memory download: NULL buffer pointer at 0x3aa4 (Emulation package 9.11.0.00128)