https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1343840/am6421-hung-in-spl

器件型号:AM6421主题中讨论的其他器件: SysConfig、 SK-AM64B、 TMDS64EVM

我正尝试推出一款 利用512MB LPDDR4内存的定制 AM6421设计。

我使用的是09.02.00.08发行版、其机器=am64xx-EVM。

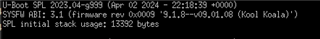

该器件似乎在 SPL 中遇到了硬故障、我怀疑这与具有2GB RAM、我的板只有512MB 的 SK-AM64有关。

我进行了以下更改、但仍然有问题。

diff --git a/arch/arm/dts/k3-am642-evm.dts b/arch/arm/dts/k3-am642-evm.dts

索引 dcd8f7ba4cf497bceb7f3e7ece5ec65711cadba8..b53c7b89bc51c57105ce6e09e34b30c699bcbdf4 100644

--a/arch/arm/dts/k3-am642-evm.dts

++ b/arch/arm/dts/k3-am642-evm.dts

@@-23、8 + 23、8 @@

内存@8000000{

device_type ="存储器";

-/* 2G RAM */

- reg =<0x00000000 0x80000000 0x00000000 0x80000000>;

+/* 512MB RAM */

+ reg =<0x00000000 0x80000000 0x00000000 0x20000000>;

};

diff --git a/arch/arm/dts/k3-am642-r5-evm.dts b/arch/arm/dts/k3-am642-r5-evm.dts

Index 57d78e449c3a33b720a2d9309d18955326699a24..cd1983057a4681ee3a95e3cbdb0ab8a37c9b7808 100644

--a/arch/arm/dts/k3-am642-r5-evm.dts

++ b/arch/arm/dts/k3-am642-r5-evm.dts

@@-23、8 + 23、8 @@

内存@8000000{

device_type ="存储器";

-/* 2G RAM */

- reg =<0x00000000 0x80000000 0x00000000 0x80000000>;

+/* 512MB RAM */

+ reg =<0x00000000 0x80000000 0x00000000 0x20000000>;

bootph-pre-ram;

};

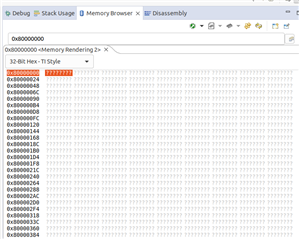

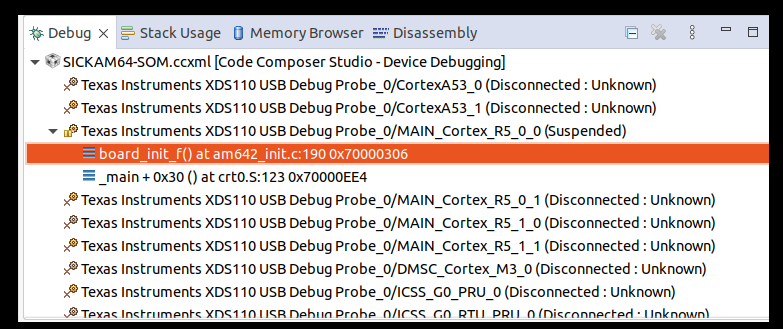

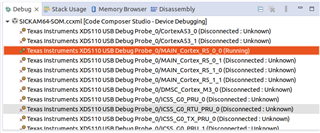

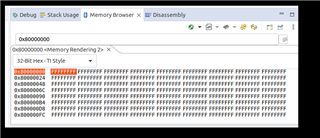

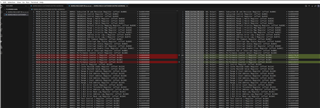

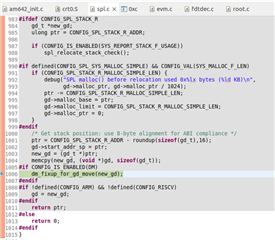

我将使用 JTAG 进行调试、并已确定哪个线路导致了硬故障。

当 memcpy 在第1004行执行时、没有复制到 new_gd 中。 处理器在1006行挂起。

我想其他一些东西还需要更新以适应我正在使用的更小 RAM 吗? 非常感谢任何帮助。

谢谢。

丹