主题中讨论的其他器件: DP83826E

您好、Champs:

硬件:PHY 83826E

SW: MCU_PLUS_SDK_am64x_09_00_00_31

硬件连接:

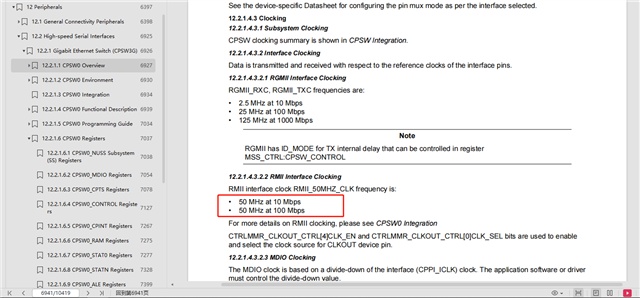

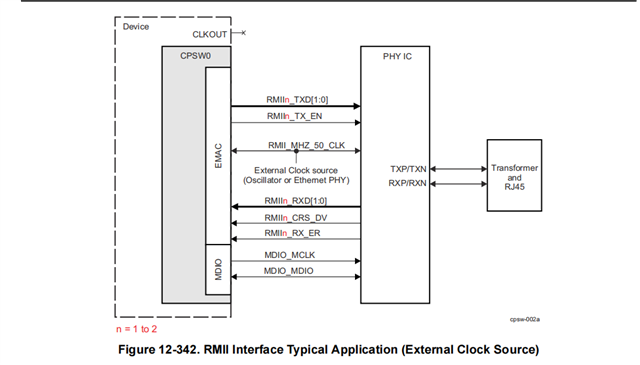

CPSW MAC ENT PORT1作为 RMII 从模式连接到83826E、外部晶体50M 连接 AM6442至 AA5引脚(即 RMII_MHz_50_CLK)和83826引脚9

测试:

通过读取 PHY 寄存器0x468、 可显示 PHY 以 RMII 从模式运行、并读取寄存器0x10、可看到 PHY 处于100M 全双工链路状态。

遇到的问题:

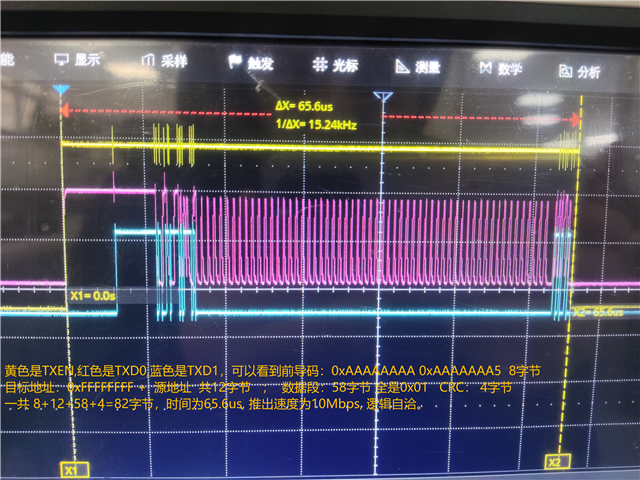

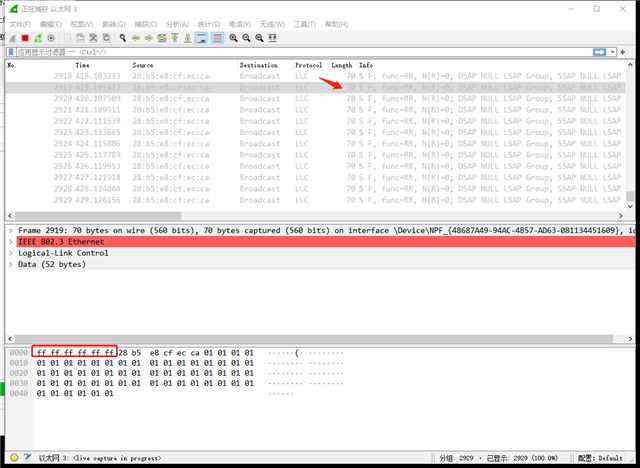

通过 CPSW CPPI 将数据转发到 ENT 端口1、以进行以太网帧数据传输。 使用示波器捕捉 PHY 芯片引脚23 (TXEN ) PHY 芯片引脚24 (TXD0) PHY 芯片引脚25 (TXD1)、并查看以太网帧前导码、目标地址、源地址、随机数据、CRC (总计82字节)、TXEN 脉冲宽度65.6us (即速度10Mbps)。

客户猜测 ENT Port1仅发送10M。 但他找不到将其更改为100m 的正确配置。

当前与 CPSW 速度相关的配置如下:(是否有任何其他可设置端口速度的配置?)

将寄存器(0x08022330)的 bit 7设置为0:10/100模式;bit 17为0:不强制进入千兆位

客户正在 使用基于 C:\ti\mcu_plus_sdk_am64x_09_00_31\examples\networking\enet_layer2_cpsw\am64x-evm 的工程。 RGMII 模式可在 EVM 上运行。 但在项目和硬件板中、需要的是 RMII 模式、因此他修改了一些配置以适合 RMII 模式。

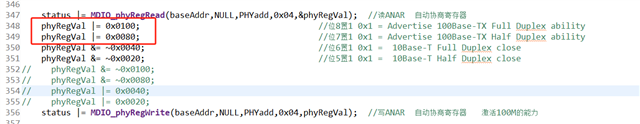

①

SoC_controlModuleUnlockMMR (SOC_DOMAIN_ID_MAIN、1);//μ 偏移量为4044,因此它落在分区1

*(vuint32_t*)(0x43004044)= 1;//cpsw0-port1 2选择RGMII 1选择RMII

*(vuint32_t*)(0x43004048)= 1;//cpsw0-port2 2选择RGMII 1选择RMII

SoC_controlModuleLockMMR (SOC_DOMAIN_ID_MAIN、1);

② SET (0x08022330) bit7为0:10/100模式 ;bit17 为0:不强制进入千兆

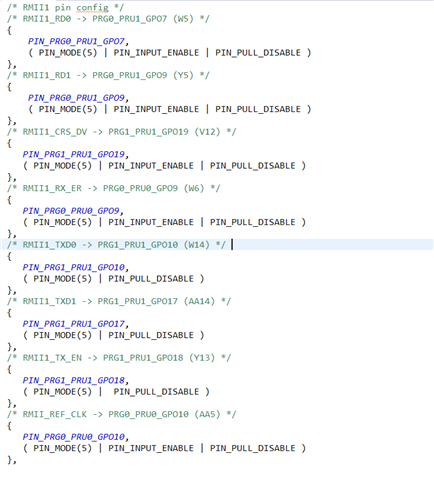

③配置 RMII:

谢谢

此致

闪耀