主题中讨论的其他器件:LMK5B33216

您好!

我正在运行 PTP 堆栈、它将主25 MHz 时钟移入 AM64来实现 ToD 对齐。

我有三个器件领导者(L)、跟随者1 (F1)和跟随者2 (F2)。

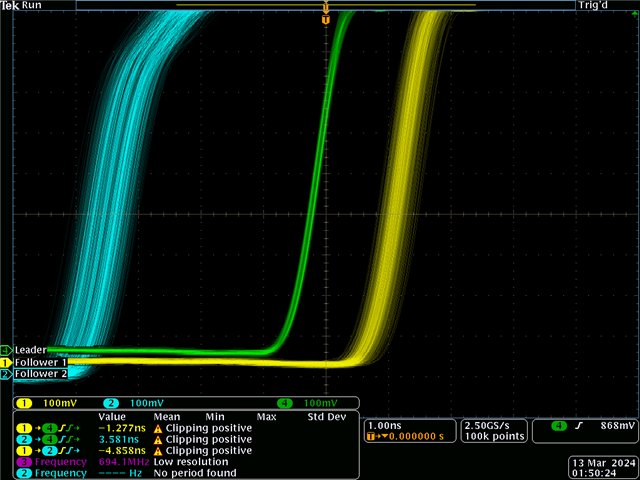

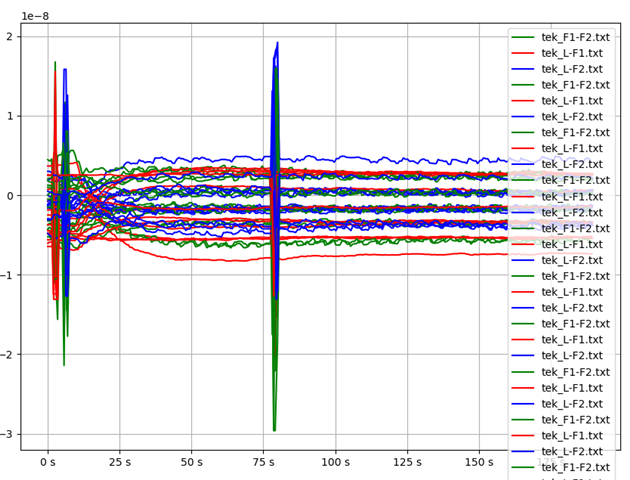

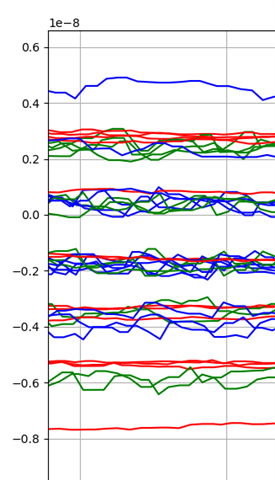

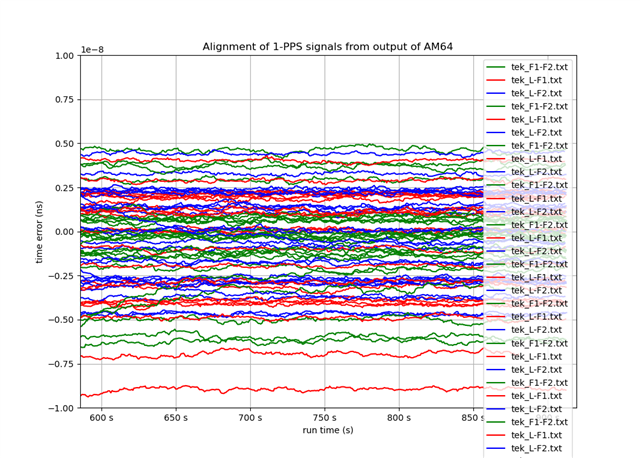

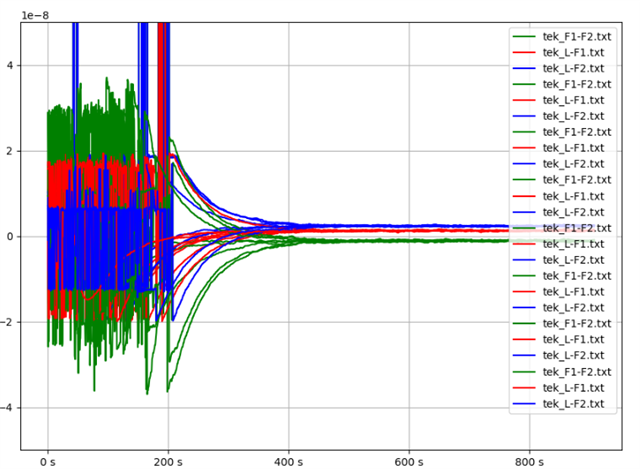

下面您可以看到 J3中 AM64 SK EVM 的一个 PPS 对齐图、其中显示了...

- 绿色作为跟随者时间与跟随者2。

- 红色、领导者与跟随者1

- 蓝色为领导者与跟随者2。

重新启动系统并重新启动 PTP 堆栈的几次运行。 对齐时的时间误差似乎为+5ns 至-10ns。

如何改进这一点?

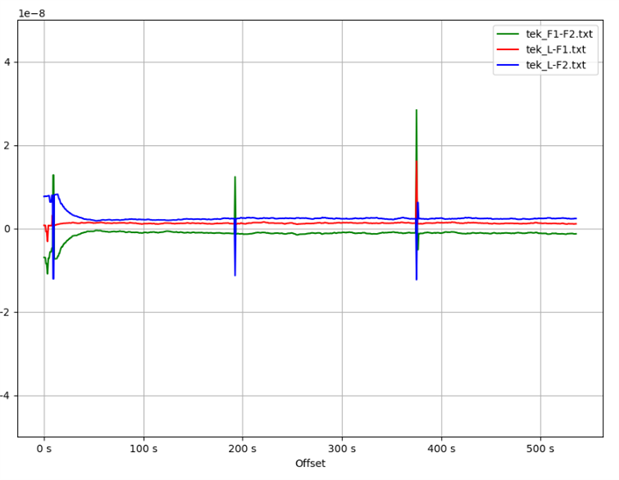

这里是一组出租数据、我只是在其中启动/停止 PTP 堆栈。 在这种情况下、对齐是确定性的、但我希望它全部更接近0。

我还做了一个测试、将1PPS 关闭/打开... 我必须执行一次此操作才能获得1PPS 以正确反映 ToD。 此操作似乎没有"采样"错误。 那么、为什么我的第一个图中存在非确定性?

testptp -i /dev/ptp0 -P 0

testptp -i /dev/ptp0 -P 1

请注意、由于我的 PTP 堆栈正在从外部执行 LMK5B33216的 DCO、我不认为下面讨论的错误会影响我... 也许我弄错了。

https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1256953/sk-am62-pps-out-not-acting-as-expected

73、

蒂莫西