您好、TI 团队、

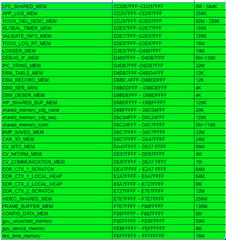

我们需要重新排列现有的2GB DDR 内存布局。

在当前现有的存储器布局中有一些空的存储器段、我尝试删除这些段并连续排列存储器。

我还尝试重新排列一些影响现有存储器部分开头和结尾的存储器部分的大小。

主要思路是将存储器从地址0xFFFFFFFF 排列至0x80000000 (向下接近顶部)。 这样我就可以在顶部获得可用存储器、并可用于将来的使用/新算法。

在以下几点中、我们需要您的输入。

1) 1)我可以在 gen_linker_mem_map.py 文件中找到一些存储区/分区、在其中可以找到其他存储区。 您能否提到除 python 脚本以外的其他文件来执行存储器媒介?

2)在现有的内存布局中,我可以在三个不同的地方看到 GHS OS 的内存,为什么? GHS OS 所需的预期存储器是什么?

3) 3)我们可以更改 MCU 域的起始地址和结束地址吗? 如果不是、为什么?

4)我们可以更改 GHS 系统的起始地址吗? 目前它是 8000000 ~ 9e000000 , 480 M.

5)我们是否可以重新排列内核引导段内存9e000000 ~ A0000000, 32M?

请查看随附的重新排列的存储器布局。

此致、

Jayasankar