This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们正尝试从 F28379D 切换到性能更高的 AM64平台。 AM64似乎是一个很好的选择、但一些测量结果让我们感到惊讶。 相同的数学计算包括:

我们发现 R5的性能令人惊讶。 200MHz Delfino 是否应在具有800MHz 的情况下实现与 ARM R5f 几乎相同的性能? 是否有办法提高 R5内核的性能(优化、启用硬件外设)?

此致、

安德烈安

您好、 Andrean:

感谢您的提问。

相同的数学计算需要:

您能提供更多的信息,你正在尝试在这里什么?

例如:

数据和代码存储在哪个存储器位置?

访问数据的方法?

此致

阿什瓦尼

尊敬的 Ashwani:

我们实现了多轴运动控制。 有三角函数、IIR 滤波器、乘法、除法等。 计算时、我们仅使用"float"类型。

代码和数据存储在 DDR RAM 中。 我们对所有数据(数组)使用随机存储器存取。 此应用程序与 FreeRTOS 一起运行。

此致、

安德烈安

您好、Andrean:

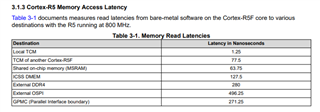

主要延迟来自存储器访问、尤其是将代码和数据放入 DDR RAM 时。 AM64x 中有三个级别的存储器:TCM、OCRAM 和 DDR。 下表列出了这些内存级别的内存访问延迟:

在 Sitara AM64x/AM243x 基准测试中、Cortex-R5存储器访问延迟(修订版 B)(TI.com)。

尝试将代码和数据、尤其是最常用的代码和数据放入 TCM 和 OCRAM 中。 请避免尽可能使用 DDR。

此致、

明

Ming 您好、

感谢您的快速回答!

我们使用 DDR、但会缓存数据和指令。 我们刚刚使用禁用的缓存运行了相同的测试。 在 R5F 上计算同样的运动需要3ms (而不是215uS)。 我们还尝试了将数据和代码放入 TCM 存储器。 R5F 的执行方式与在启用了高速缓存的 DDR 中相同。

是否还有其他任何东西可以帮助提高 R5内核的性能?

此致、

安德烈安

您好, Andrean С ć,

您能否共享或检查存储器区域的 linker.cmd 文件和 SysConfig 文件设置?

以下是一些指导原则:

此致

阿什瓦尼

尊敬的 Ashwani:

这是链接器文件:

/* This is the stack that is used by code running within main()

* In case of NORTOS,

* - This means all the code outside of ISR uses this stack

* In case of FreeRTOS

* - This means all the code until vTaskStartScheduler() is called in main()

* uses this stack.

* - After vTaskStartScheduler() each task created in FreeRTOS has its own stack

*/

--stack_size=8192

/* This is the heap size for malloc() API in NORTOS and FreeRTOS

* This is also the heap used by pvPortMalloc in FreeRTOS

*/

--heap_size=200000

-e_vectors /* This is the entry of the application, _vector MUST be placed starting address 0x0 */

/* This is the size of stack when R5 is in IRQ mode

* In NORTOS,

* - Here interrupt nesting is enabled

* - This is the stack used by ISRs registered as type IRQ

* In FreeRTOS,

* - Here interrupt nesting is enabled

* - This is stack that is used initally when a IRQ is received

* - But then the mode is switched to SVC mode and SVC stack is used for all user ISR callbacks

* - Hence in FreeRTOS, IRQ stack size is less and SVC stack size is more

*/

__IRQ_STACK_SIZE = 256;

/* This is the size of stack when R5 is in IRQ mode

* - In both NORTOS and FreeRTOS nesting is disabled for FIQ

*/

__FIQ_STACK_SIZE = 256;

__SVC_STACK_SIZE = 4096; /* This is the size of stack when R5 is in SVC mode */

__ABORT_STACK_SIZE = 256; /* This is the size of stack when R5 is in ABORT mode */

__UNDEFINED_STACK_SIZE = 256; /* This is the size of stack when R5 is in UNDEF mode */

SECTIONS

{

.vectors : {

} > R5F_VECS , palign(8)

GROUP : {

.text.hwi : {

} palign(8)

.text.cache : {

} palign(8)

.text.mpu : {

} palign(8)

.text.boot : {

} palign(8)

.text:abort : {

} palign(8)

} > MSRAM

GROUP : {

.text : {

} palign(8)

.rodata : {

} palign(8)

} > DDR

GROUP : {

.data : {

} palign(8)

} > DDR

GROUP : {

.bss : {

} palign(8)

RUN_START(__BSS_START)

RUN_END(__BSS_END)

.sysmem : {

} palign(8)

.stack : {

} palign(8)

} > DDR

GROUP : {

.irqstack : {

. = . + __IRQ_STACK_SIZE;

} align(8)

RUN_START(__IRQ_STACK_START)

RUN_END(__IRQ_STACK_END)

.fiqstack : {

. = . + __FIQ_STACK_SIZE;

} align(8)

RUN_START(__FIQ_STACK_START)

RUN_END(__FIQ_STACK_END)

.svcstack : {

. = . + __SVC_STACK_SIZE;

} align(8)

RUN_START(__SVC_STACK_START)

RUN_END(__SVC_STACK_END)

.abortstack : {

. = . + __ABORT_STACK_SIZE;

} align(8)

RUN_START(__ABORT_STACK_START)

RUN_END(__ABORT_STACK_END)

.undefinedstack : {

. = . + __UNDEFINED_STACK_SIZE;

} align(8)

RUN_START(__UNDEFINED_STACK_START)

RUN_END(__UNDEFINED_STACK_END)

} > MSRAM

GROUP : {

.ARM.exidx : {

} palign(8)

.init_array : {

} palign(8)

.fini_array : {

} palign(8)

} > MSRAM

.bss.user_shared_mem (NOLOAD) : {

} > USER_SHM_MEM

.bss.log_shared_mem (NOLOAD) : {

} > LOG_SHM_MEM

.bss.ipc_vring_mem (NOLOAD) : {

} > RTOS_NORTOS_IPC_SHM_MEM

.bss.nocache (NOLOAD) : {

} > NON_CACHE_MEM

GROUP : {

motion : {

} align(8)

} > R5F_TCMB0

}

MEMORY

{

R5F_VECS : ORIGIN = 0x0 , LENGTH = 0x40

R5F_TCMA : ORIGIN = 0x40 , LENGTH = 0x7FC0

R5F_TCMB0 : ORIGIN = 0x41010000 , LENGTH = 0x8000

NON_CACHE_MEM : ORIGIN = 0x70060000 , LENGTH = 0x8000

MSRAM : ORIGIN = 0x70080000 , LENGTH = 0x40000

USER_SHM_MEM : ORIGIN = 0x701D0000 , LENGTH = 0x80

LOG_SHM_MEM : ORIGIN = 0x701D0080 , LENGTH = 0x3F80

RTOS_NORTOS_IPC_SHM_MEM : ORIGIN = 0x701D4000 , LENGTH = 0xC000

FLASH : ORIGIN = 0x60100000 , LENGTH = 0x80000

DDR : ORIGIN = 0x80000000 , LENGTH = 0x1F0000

/* For memory Regions not defined in this core but shared by other cores with the current core */

}

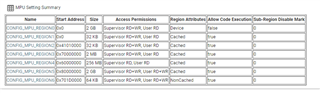

这是 MPU 配置:

此致、

安德烈安

您好、 Andrean:

谢谢您的博客。

您能否同时共享生成的 memory_map 文件?

此致

阿什瓦尼

尊敬的 Ashwani:

是的、当然可以。

此致、

安德烈安

感谢 Andrean:

请允许我花点时间来回顾并回复您。

此致

阿什瓦尼

尊敬的 Ashwani:

您有时间查看我的文件吗?

此致、

安德烈安

您好, Andrean С ć,

很抱歉响应延迟。

我仍在内部讨论这一点。

请允许我再多花点时间。

感谢您的耐心等待。

此致

阿什瓦尼

您好、Andrean:

你能否在 linker.cmd 中尝试以下命令?

添加

MSRAM1:origin = 0x700C0000,length = 0x100000

将 DDR 的所有引用更改为 MSRAM1

此致、

明

Ming 您好、

如果我将 所有内容都添加到 MSRAM 中、执行时间会缩短:

- 180uS 未优化

- 80us 与第三优化

感谢您的帮助!

此致、

安德烈安