主题中讨论的其他器件:TDA2

您好!

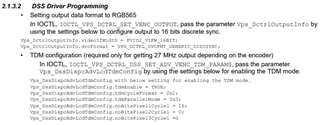

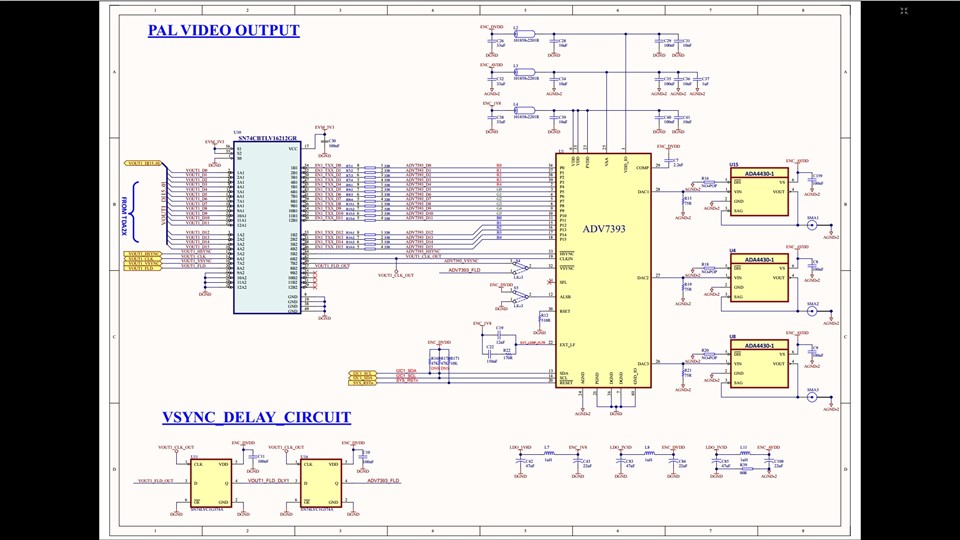

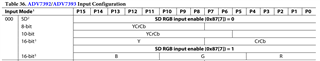

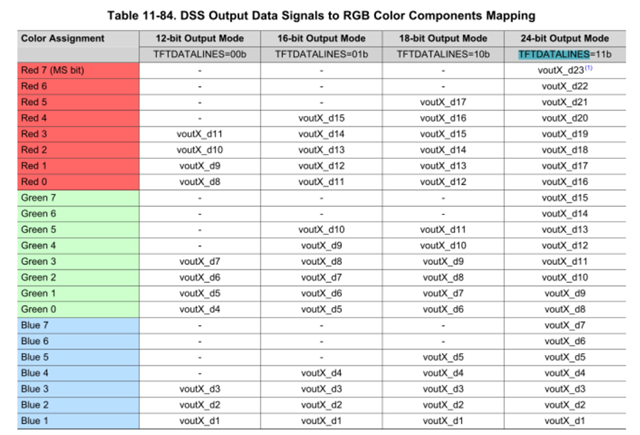

我想使用 ADV7393从 TDA2x DSS 的视频输出端口获取 PAL 输出。 我已经制作了原理图。 我只是想回顾一下该原理图。 我已经将 D0到 D15连接到编码器的 P0到 P15。 我正在使用的复位由一个可编程延迟 IC 生成。 HS 直接从 VOUT1到 ADV 的 HS。 在 VS 方面、我已经按照应用手册的建议添加了 D 触发器(用于延迟 FLD)、并将输出连接到了 ADV 的 VS。 请查看我的原理图(我已随附)并建议任何更改(如有)、以便我最终确定我的设计。

请参阅附件:

请参阅附件: