主题中讨论的其他器件:TDA4VH、TDA4VM

您好、Champs:

客户希望 在 tda4vh-sdk8.6中输入100Mhz 的 REFCLK。 他使用了下面的补丁、但它不起作用。

[常见问题解答] TDA4VM:TDA4VM/DRA829V:从外部路由 PCIe 参考时钟-处理器论坛-处理器- TI E2E 支持论坛

谢谢

此致

闪耀

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Champs:

客户希望 在 tda4vh-sdk8.6中输入100Mhz 的 REFCLK。 他使用了下面的补丁、但它不起作用。

[常见问题解答] TDA4VM:TDA4VM/DRA829V:从外部路由 PCIe 参考时钟-处理器论坛-处理器- TI E2E 支持论坛

谢谢

此致

闪耀

尊敬的 Shine:

我看到 TDA4VH 就是在使用的 SoC。 您是否可以尝试使用以下补丁来使用内部 REFCLK?

e2e.ti.com/.../enable_5F00_internal_5F00_ref_5F00_clock_5F00_out_5F00_pcie1_5F00_j784s4.patch

此致、

大沼市

您好、 Takuma、

非常感谢。

diff --git a/board-support/linux-kernel/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts b/board-support/linux-kernel/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

索引492975144..8a3f17450 100644

---a-board-support/linux-kernel/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

++ b/board-support/linux-kernel/arch/arm64/boot/dts/ti/k3-j784s4-evm.dts

@@-729,7 +729,7 @@&serdes1{

状态="可以";

Serdes1_PCIe_link:phy@0{

寄存器=<0>;

- cdns, num-lannes =<2>;

+ CDN、num-Lanes =<4>;

#phy-cells =<0>;

CDN、phy-type = ;

重置=<&SerDes_wiz1>、<&SerDes_wiz1 2>;

@@-745,11 +745,14 @@&pcie0_RC{

RESET-GPIO =<和 exp1 6 GPIO_ACTIVE_HIGH>;

PHY =<&serdes1_pci_link>;

phy-names ="PCIe-phy";

+状态="可以";

+

};

&pcie0_ep{

PHY =<&serdes1_pci_link>;

phy-names ="PCIe-phy";

+ status ="已禁用";

};

&pcie1_rc{

@@-783、7 + 786、8 @@&SerDes_ln_ctrl{

, ,

, ,

, ,

- , ;

+ , ,

+ , ;

};

&main_udmass_inta{

diff --git a/board-support/linux-kernel/drivers/phy/cadence/phy-cadence-torrent.c b/board-support/linux-kernel/drivers/phy/cadence-candence-torrent.c

索引 f04619634..34b44c31f 100644

--a-board-support/linux-kernel/drivers/phy/cadence/phy-cadence-torrent.c

++ b/board-support/linux-kernel/drivers/phy/cadence/phy-cadence-torrent.c

@@-2780,6 +2780,27 @@静态 int cdns_torrent_phy_probe (struct platform_device *pdev)

IF (RET)

goto put_lnk_rst;

}

+/*解锁分区7 : 8000h 到9FFFh */

+ writel (0x68EF3490、ioremap (0x011D008、0x4));/* LOCK7_KICK0 */

+ writel (0xD172BC5A、ioremap (0x011D00C、0x4));/* LOCK7_KICK1 */

+/*解锁分区1 : 4000h 到5FFFh */

+ writel (0x68EF3490、ioremap (0x00105008、0x4));/* lock1_KICK0 */

+ writel (0xD172BC5A、ioremap (0x0010500C、0x4));/* lock1_KICK1 */

+

+/*解锁分区2 : 8000h 至9FFFh */

+ writel (0x68EF3490、ioremap (0x00109008、0x4));/* LOCK2_KICK0 */

+ writel (0xD172BC5A、ioremap (0x0010900C、0x4));/* LOCK2_KICK1 */

+

+

+/*启用 ACSPCIe0 PAD 0和1 */

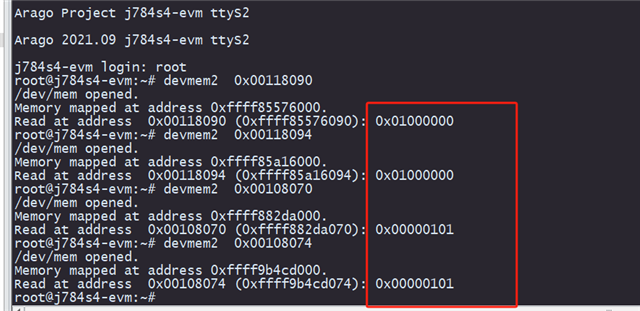

+ writel (0x01000000、ioremap (0x00118090、0x4));

+/*启用 ACSPCIe1 PAD 0和1 */

+ writel (0x01000000、ioremap (0x00118094、0x4));

+

+/* PCIe_REFCLK0_CLKSEL:EN + MAIN_PLL2_HSDIV4_CLKOUT */

+ writel (0x00000101、ioremap (0x00108070、0x4));

+/* PCIE_REFCLK1_CLKSEL:EN + MAIN_PLL2_HSDIV4_CLKOUT */

+ writel (0x00000101、ioremap (0x00108074、0x4));

phy_provider = devm_of_phy_provider_register (dev、of_phy_simple_xlate);

if (is_ERR (phy_provider)){

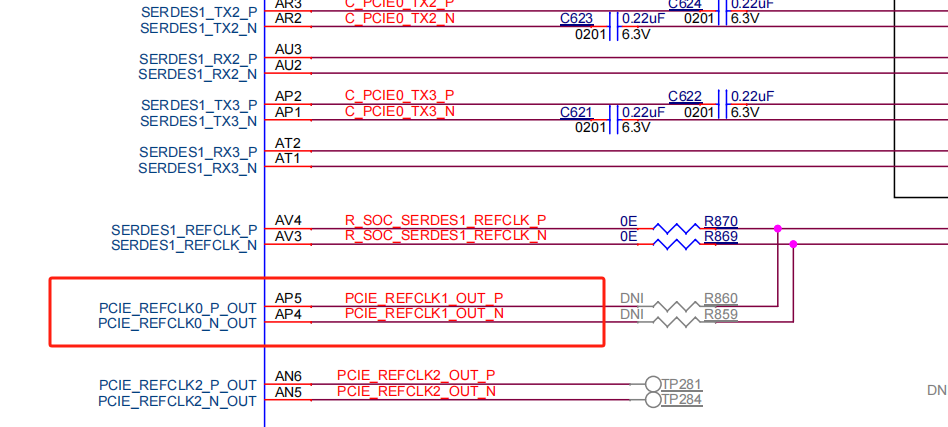

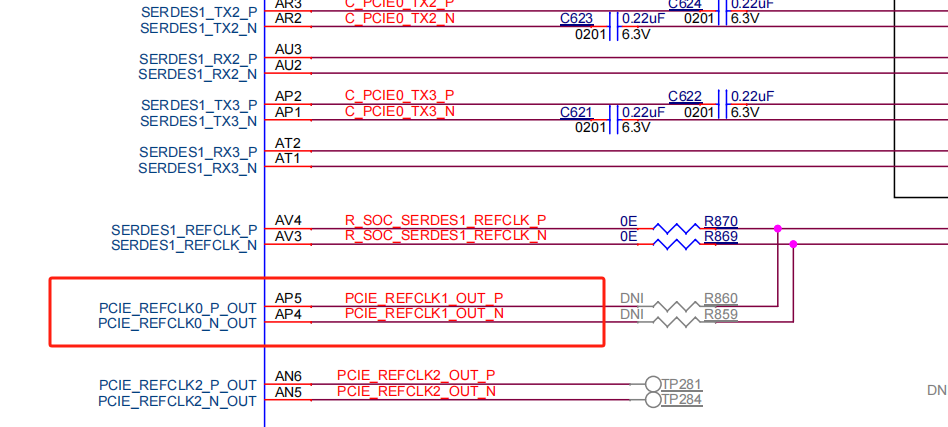

测试 R860 R859、电压从0变为1.8V、频率正在变化、不接近100MHz

注意:使用 VH EVM 板

谢谢

此致

闪耀

您好、 Takuma、

要澄清,是否安装了 R860 R859? [/报价]R860 R859未安装。

以及是否看到电压正在切换但不在100MHz 上的行为?

频率不正确。 波似乎是噪声波。

e2e.ti.com/.../PCIE_5F00_REFCLK1_5F00_P_5F00_OUT.mp4振幅 变化是由于位24=1、如果设置为1、则为1.8V、如果设置为0、则为0V。

/* PCIe_REFCLK0_CLKSEL:EN + MAIN_PLL2_HSDIV4_CLKOUT */

writel (0x00000101、ioremap (0x00108070、0x4));

/* PCIe_REFCLK1_CLKSEL:EN + MAIN_PLL2_HSDIV4_CLKOUT */

writel (0x00000101、ioremap (0x00108074、0x4));

客户发现您选择的路径为 MAIN_PLL2_HSDIV4_CLKOUT,root 用户@j784s4-evm:~# devmem2 0x682090

/dev/mem 打开。

存储器映射在地址0xffb5d19000。

在地址0x00682090 (0xFFfb5d19090)处读取:0x00008011

root 用户@j784s4-evm:~# devmem2 0x682030

/dev/mem 打开。

存储器映射在地址0xffffff985cb000。

在地址0x00682030 (0xFFff985cb030)处读取:0x0000005D

root 用户@j784s4-evm:~# devmem2 0x682034

/dev/mem 打开。

存储器映射在地址0xffb9ec5000。

在地址0x00682034 (0xffb9ec5034)处读取:0x00C00000

root 用户@j784s4-evm:~#19.2M× 93.75=1800M1800M/18 = 100MMAIN_PLL2_HSDIV4_CLKOUT=100MPCIe_REFCLK1_P_OUT 是否与串行器/解串器相关?只是由系统输出?[/quote]

谢谢

此致

闪耀

您好、 Takuma、

非常感谢。

SDK7.3补丁:

/cfs-file/__key/communityserver-discussions-components-files/791/0001_2D00_route_2D00_clock_2D00_externally.patch

regmap_field_write (cdns_phy->phy_pma_CMN_ctrl_rcv_out_en、0x3);

regmap_field_write (cdns_phy->cmn_plllc_clk1_en、0x1);

regmap_field_write (cdns_phy->cmn_plllc_clk1outdiv、0x2e);

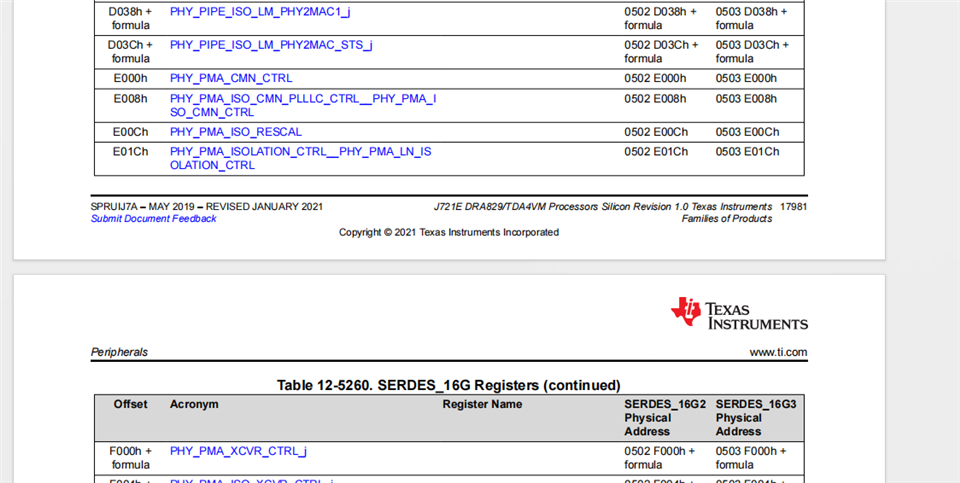

根据代码、寄存器偏移量应为 e09a、但寄存器说明中未提及。 现在还不是公开的吗?

谢谢

此致

闪耀

尊敬的 Shine:

某些寄存器可能不在 TRM 中、因为这些寄存器 直接取自 Cadence 的某些 IP 文档。

不过、您引用的补丁适用于 TDA4VM、它具有称为 Sierra 的不同 SERDES、而 TDA4VH 具有 Torrent SERDES、因此两者的 SERDES 寄存器偏移会不同。 澄清一下、该器件是用作 TDA4VH 还是用作 TDA4VM?

此致、

大沼市

尊敬的 Shine:

我现在再次回顾一些开放的旧线程。 该主题帖是否仍处于打开状态?

如果是、我已经创建了一个常见问题解答、其中处理了第二个 PCIe 端口不输出100MHz REFCLK: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1230896/faq-j784s4xevm-how-to-enable-second-pcie-slot-for-two-ssd-cards

如常见问题解答中所述、在9.0 SDK 及后续版本中、有一个补丁可以为第二个 PCIe 端口启用内部 REFCLK、以便为100MHz 端口提供 PCIe REFCLK、因此无需更改硬件。

但是、如果您希望切换 PCIe0实例以使用内部时钟、则需要进行软件更改和硬件更改、因为端口在物理上连接到外部参考时钟而不是内部时钟。

此致、

大沼市