主题中讨论的其他器件:SK-AM62A-LP

在运行 AI 演示后、我碰巧注意到它们不会以接近全速的任何速度运行。 如何调试为什么选择第二条形图(什么核心?) 是100%吗?

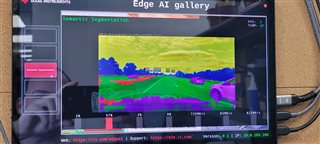

来自我们开发套件的图像:

在运行09.01的 EVM 上 :

图像阐明:FPS 2-3、温度42、几乎所有内核都处于空闲状态。 演示看起来很流畅、是幻灯片放映

对象检测: FPS 30 ,温度43,内核30-50%已使用。 演示看起来很顺利。 DDR RD 2700Mb/s、DDR WR 401Mb/s、DDR 总计3170Mb/s

语义分段: FPS 18 ,温度44,内核20-50%使用。 演示看起来很平滑、尽管 HDMI 输出似乎出现干扰

多通道:FPS 25、温度45。 演示看起来很顺利

在 AM62A 开发套件09.01上 :

图像分类:FPS 2-3、temp 46、几乎所有内核均空闲。 演示看起来很流畅、是幻灯片放映

对象检测: FPS 3 ,温度46,c7x_1 94%(其它2%)。 演示看起来很落后。 DDR RD 800Mb/s、DDR WR 33Mb/s、DDR 总计830Mb/s

语义分段: FPS 2 ,温度47,c7x_1 97%(其它2%)。 演示看起来很糟糕

多通道:FPS 1、温度37。 演示看起来很糟糕

注意:不确定演示为什么会被切断、EVM 和我们的电路板上都会发生这种情况。 似乎取决于显示器,但两个报告都是1920x1080