您好、TI 专家!

关于 I2C 接口、我有以下疑问:

- 需要有关可用 I2C 接口数量的信息。

- 当用作 I2C 接口而不用作 I2C 接口时、I2C 接口的终端。

- 任何其他建议/指南

- 有关将 SoC 非失效防护 I2C 连接到在 SoC-ex PMIC 之前加电的器件的任何问题

- 使用 I2C 接口时需要考虑的任何异常。

- I2C 接口能否用于连接支持 SMBus 或 PMBus 的器件

请告诉我您的想法。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、TI 专家!

关于 I2C 接口、我有以下疑问:

请告诉我您的想法。

板设计师、您好!

有关 I2C 接口相关查询、请参阅以下输入。

此器件包含6个多控制器内部集成电路(I2C)控制器。 每个 I2C 控制器的设计与飞利浦 I2C 总线 技术规范版本2.1兼容。 然而、器件 IO 并不完全符合 I2C 电气规范。

开漏缓冲器类型 I2C 接口- MCU_I2C0和 WKUP_I2C0

这些 I2C 接口是开漏型 IO。 这些 I2C 接口为失效防护 IO 终端。

连接到这些端口的 I2C 信号的上升和下降时间不得超过 0.8 V/ns 的压摆率(或8E+7V/s)。 此限制比 I2C 规范中定义的最短下降时间限制更为严格。 因此、可能有必要为 I2C 信号添加额外的电容(RC)、以缩短上升和下降时间、使其不超过0.8 V/ns 的压摆率。

请参阅以下内容

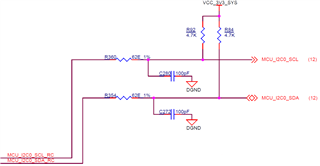

参考:AM62P SK 原理图

注意: 电路板设计人员负责实施必要(必需)的任何预防措施、以确保 其定制电路板设计不会违反数据表中提到(指定)的要求。 可将原理图设计和检查清单或 SK 原理图实现中提供的建议作为一个起点。

LVCMOS 缓冲器类型 I2C 接口- I2C0、I2C1、I2C2和 I2C3

这些 I2C 接口是 LVCMOS IO 类型。 连接这些端口上使用的 LVCMOS IO、以便它们模拟开漏输出。

开漏缓冲器类型 I2C 接口 - MCU_I2C0和 WKUP_I2C0

请参阅数据表中的引脚连接要求。

当配置为 I2C 或 GPIO 时、建议端接这些接口。 当 IO 配置为输入并由上电时的推挽输入驱动时、可以取消填充终端

LVCMOS 缓冲器类型 I2C 接口- I2C0、I2C1、I2C2和 I2C3

当配置为 I2C 接口时、建议使用上拉电阻。 由于这些 IO 是 LVCMOS 类型的、建议将上拉电阻与最短接线柱相连。 当配置为 GPIO 时、根据用例、可以提供外部拉取或使用内部拉取。

I2C3具有一个或多个信号、这些信号可以多路复用到多个引脚。 时序仅对称为 IOSET 的特定引脚组合有效。 此接口的有效引脚组合或 IOSET 在 SysConfig-PinMux 工具中定义。

请参阅器件特定数据表的以下部分。

7.8.1 I2C 开漏和失效防护(I2C OD FS)电气特性

4.有关将 SoC 非失效防护 I2C 连接到在 SoC-ex PMIC 之前加电的器件的任何问题

连接的 PMIC IO 是否是真正的开漏 I2C IO? 如果可以、与该 I2C 端口关联的上拉电阻是否与用于为 SoC I2C 示例 I2C0 IO 供电的电源相同? 如果这两个问题的答案都是肯定的、那么我们不应该有失效防护问题。

在为 IO 加电之前、这些 I2C 信号是否连接了其他任何东西、这些信号可能会为 I2C0引脚提供电位?

仅当连接的器件可能在 SoC IO 接收电源之前应用电势时、我们才会考虑失效防护。 如果无法做到、我们不会有任何失效防护问题。

5.使用 I2C 接口时需要考虑的任何例外情况。

请参阅数据表的第6.11.5.13节 I2C。

通读 I2C0、I2C1、I2C2和 I2C3 的异常部分;MCU_I2C0和 WKUP_I2C0的异常部分

可以使用 I2C 接口连接支持 SMBus 或 PMBus 的器件

在这些处理器系列中实现的 I2C 模块不支持 SM 总线或 PM 总线

此致、

Lavanya M R