请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AM6548 团队、

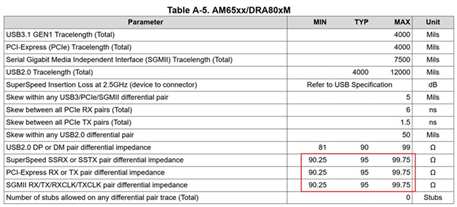

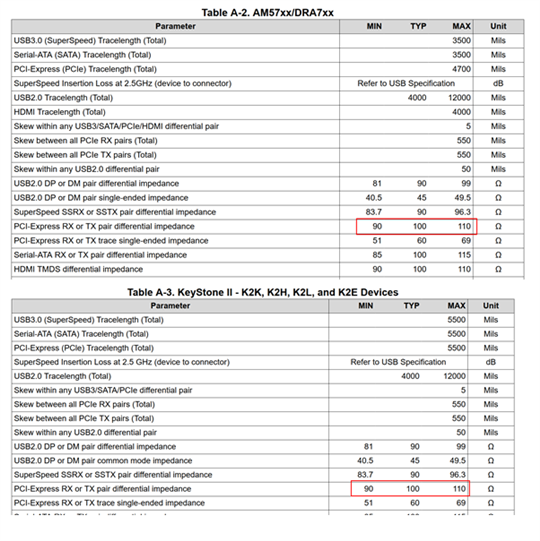

在 "AM65x"应用手册:高速接口布局指南"中,对 AM6548的 PCIe 差分阻抗控制的要求是95Ω±5%,在 AM57x 和 K2中,该值是 ±10%,

客户想知道原因、以及他们是否可以使用 ±10%、因为 更严格的标准会导致 PCB 成本显著增加。

-谢谢

托马斯

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Thomas、

AM65x 建议是尝试适应在与我们 EVM 上完成的相同通道上使用 USB3和 PCIe Gen3。 然而、需要更严格阻抗控制的 PCIe Gen3已被器件勘误表 i2104弃用。

如果此客户仅使用 PCIe、并且仅处于 Gen1和/或 Gen2模式、则该通道可支持100欧姆(+/- 10%)的目标差分阻抗。 请确保在制造之前对最终设计进行仿真、因为可能需要根据特定于电路板的变量进行更严格的阻抗控制、例如通道长度、PCB 基板材料、连接器、链路伙伴、过孔、 等等