我们在 c6678 DSP 上运行、并将 CCS8与 CGT C6000_8.3.2配合使用、并且可以看到写入 boot_magic_address 时.text 段似乎损坏了。

extern volatile cregister unsigned int DNUM;

uint32_t getDspId (){

返回 DNUM;

}

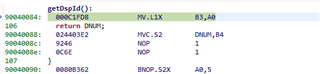

core0写入引导魔术地址之前的汇编

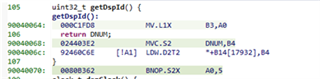

写入内核1的引导魔法地址后、从内核0开始汇编所有内核、但0暂停

当 core1的第一次内核写入 boot_magic_address 时、asm 代码会同时更改。 据我所知、在写入 IPC 后释放这些内核之前、引导魔法 addr 实际上并没有太大作用。

#define MAGAIC_ADDR 0x87fffc

#define boot_magic_ADDR (x)(MAGIC_ADDR +(1<<28)+(x<<24))

写入 boot_magic_address 时是否会进行更多处理? 写入 boot_magic_address 时、我看到程序的.text 段已修改其存储器、特别是有一个字设置为 c_int00值。 写入的地址没有位于更改的.text 存储器附近的位置(一个实例中为0x9004007C)