请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TDA4VM 按照指南在 Ubuntu 22.04上设置 CCS

脚本控制台:

js:> loadJSfile ("/home/tony/ti/ti-processor-sdk-rtos-j721e-evm-09_02_00_05/pdk_jacinto_09_02_00_30/packages/ti/drv/sciclient/tools/ccsLoadDmsc/j721e/launch.js")

Connecting to DMSC_Cortex_M3_0!

Fill R5F ATCM memory...

Writing While(1) for R5F

Loading DMSC Firmware ... /ti/ti-processor-sdk-rtos-j721e-evm-09_02_00_05/pdk_jacinto_09_02_00_30/packages/ti/drv/sciclient/soc/sysfw/binaries/ti-fs-firmware-j721e-gp.bin

DMSC Firmware Load Done...

DMSC Firmware run starting now...

Running the DDR configuration... Wait till it completes!

Connecting to MCU Cortex_R5_0!

WKUP Boot Mode is 56

Main Boot Mode is 65

Disable MCU Timer for ROM clean up

Error evaluating "GEL_Load("/ti/ti-processor-sdk-rtos-j721e-evm-09_02_00_05/pdk_jacinto_09_02_00_30/packages/ti/drv/sciclient/tools/ccsLoadDmsc/j721e/sciclient_ccs_init_mcu1_0_release.xer5f")": Unable to open file: /ti/ti-processor-sdk-rtos-j721e-evm-09_02_00_05/pdk_jacinto_09_02_00_30/packages/ti/drv/sciclient/tools/ccsLoadDmsc/j721e/sciclient_ccs_init_mcu1_0_release.xer5f

at GEL_Load("/ti/ti-processor-sdk-rtos-j721e-evm-09_02_00_05/pdk_jacinto_09_02_00_30/packages/ti/drv/sciclient/tools/ccsLoadDmsc/j721e/sciclient_ccs_init_mcu1_0_release.xer5f") (/home/tony/ti/ti-processor-sdk-rtos-j721e-evm-09_02_00_05/pdk_jacinto_09_02_00_30/packages/ti/drv/sciclient/tools/ccsLoadDmsc/j721e/launch.js#153)

js:>

控制台输出停止在下面,我认为问题是路径:/ti/ti-processor-sdk-rtos-j721e-evm-09_02_00_05 ,有时它从系统根目录开始:/home/user ,有时从用户的根目录开始。

DMSC_Cortex_M3_0: GEL Output: Setting DDR PLL + HSDIV to 933MHz DMSC_Cortex_M3_0: GEL Output: DDR PLL Calibration Control MMR value: 0x80170000 DMSC_Cortex_M3_0: GEL Output: DDR PLL Calibration Control MMR value: 0x80000E17 DMSC_Cortex_M3_0: GEL Output: DDR PLL + HSDIV set to 933MHz. DMSC_Cortex_M3_0: GEL Output: Frequency change request type 2 received from controller DMSC_Cortex_M3_0: GEL Output: Setting DDR PLL + HSDIV to 933MHz DMSC_Cortex_M3_0: GEL Output: DDR PLL Calibration Control MMR value: 0x80170000 DMSC_Cortex_M3_0: GEL Output: DDR PLL Calibration Control MMR value: 0x80000E18 DMSC_Cortex_M3_0: GEL Output: DDR PLL + HSDIV set to 933MHz. DMSC_Cortex_M3_0: GEL Output: --->>> All frequency change requests have completed... <<<--- DMSC_Cortex_M3_0: GEL Output: --->>> LPDDR4 Initialization is DONE! <<<--- MCU_Cortex_R5_0: GEL: Unable to open file: /ti/ti-processor-sdk-rtos-j721e-evm-09_02_00_05/pdk_jacinto_09_02_00_30/packages/ti/drv/sciclient/tools/ccsLoadDmsc/j721e/sciclient_ccs_init_mcu1_0_release.xer5f

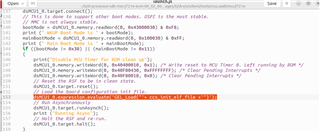

我更改了用绝对路径替换的行、然后它可以执行到下一个类似的加载固件行。

if ((bootMode != 0x38) || (mainBootMode != 0x11))

{

print("Disable MCU Timer for ROM clean up");

dsMCU1_0.memory.writeWord(0, 0x40400010, 0x1); /* Write reset to MCU Timer 0. Left running by ROM */

dsMCU1_0.memory.writeWord(0, 0x40F80430, 0xFFFFFFFF); /* Clear Pending Interrupts */

dsMCU1_0.memory.writeWord(0, 0x40F80018, 0x0); /* Clear Pending Interrupts */

// Reset the R5F to be in clean state.

dsMCU1_0.target.reset();

// Load the board configuration init file.

//dsMCU1_0.expression.evaluate('GEL_Load("'+ ccs_init_elf_file +'")');

dsMCU1_0.expression.evaluate('GEL_Load("/home/tony/ti/ti-processor-sdk-rtos-j721e-evm-09_02_00_05/pdk_jacinto_09_02_00_30/packages/ti/drv/sciclient/tools/ccsLoadDmsc/j721e/sciclient_ccs_init_mcu1_0_release.xer5f")');

// Run Asynchronously

dsMCU1_0.target.runAsynch();

print ("Running Async");

// Halt the R5F and re-run.

dsMCU1_0.target.halt();

}

js:> loadJSfile ("/home/tony/ti/ti-processor-sdk-rtos-j721e-evm-09_02_00_05/pdk_jacinto_09_02_00_30/packages/ti/drv/sciclient/tools/ccsLoadDmsc/j721e/launch.js")

Connecting to DMSC_Cortex_M3_0!

Fill R5F ATCM memory...

Writing While(1) for R5F

Loading DMSC Firmware ... /ti/ti-processor-sdk-rtos-j721e-evm-09_02_00_05/pdk_jacinto_09_02_00_30/packages/ti/drv/sciclient/soc/sysfw/binaries/ti-fs-firmware-j721e-gp.bin

DMSC Firmware Load Done...

DMSC Firmware run starting now...

Running the DDR configuration... Wait till it completes!

Connecting to MCU Cortex_R5_0!

WKUP Boot Mode is 56

Main Boot Mode is 65

Disable MCU Timer for ROM clean up

Running Async

Running the board configuration initialization from R5!

Running DDR Memory Checks....

Clearing CLEC Secure Claim...

######################################################################################

Loading Sciserver Application on MCU1_0. This will service RM/PM messages

If you do not want this to be loaded update the launch script to make loadSciserverFlag = 0

If you want to load and run other cores, please run the MCU1_0 core after Sciserver is loaded.

######################################################################################

Error evaluating "GEL_Load("/ti/ti-processor-sdk-rtos-j721e-evm-09_02_00_05/pdk_jacinto_09_02_00_30/packages/ti/drv/sciclient/tools/ccsLoadDmsc/j721e/sciserver_testapp_freertos_mcu1_0_release.xer5f")": Unable to open file: /ti/ti-processor-sdk-rtos-j721e-evm-09_02_00_05/pdk_jacinto_09_02_00_30/packages/ti/drv/sciclient/tools/ccsLoadDmsc/j721e/sciserver_testapp_freertos_mcu1_0_release.xer5f

at GEL_Load("/ti/ti-processor-sdk-rtos-j721e-evm-09_02_00_05/pdk_jacinto_09_02_00_30/packages/ti/drv/sciclient/tools/ccsLoadDmsc/j721e/sciserver_testapp_freertos_mcu1_0_release.xer5f") (/home/tony/ti/ti-processor-sdk-rtos-j721e-evm-09_02_00_05/pdk_jacinto_09_02_00_30/packages/ti/drv/sciclient/tools/ccsLoadDmsc/j721e/launch.js#222)

js:>

我的问题:只有我有这个问题? 您这边可以吗?