主题中讨论的其他器件:TDA4VH

工具与软件:

大家好:

在 TDA4VH 上电时序测试中、我们发现 DDR 的复位引脚波形如下所示、波动20mV。 该电压处于 DDR 复位引脚的高电平阈值范围内、抖动在 TDA4VH 的冷复位变为高电平后消失。 我们在 TP702点进行测试、并且对于所有四个 DDR 波形都是如此。 DDR 型号:MT53E2G32D4DE-046 AAT:CD

请帮助确认此问题的原因。 我认为这个变化对于在冷复位前 TDA4的启动没有影响、但是我们需要 TI 的确认。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

大家好:

在 TDA4VH 上电时序测试中、我们发现 DDR 的复位引脚波形如下所示、波动20mV。 该电压处于 DDR 复位引脚的高电平阈值范围内、抖动在 TDA4VH 的冷复位变为高电平后消失。 我们在 TP702点进行测试、并且对于所有四个 DDR 波形都是如此。 DDR 型号:MT53E2G32D4DE-046 AAT:CD

请帮助确认此问题的原因。 我认为这个变化对于在冷复位前 TDA4的启动没有影响、但是我们需要 TI 的确认。

您好!

[quote userid="589801" url="~/support/processors-group/processors/f/processors-forum/1370226/tda4vh-q1-tda4vh-ddr-reset-waveform 通过 TDA4VH 的冷复位转换为高电平后、抖动消失。是否正在进行此测量时 TDA4VH 器件处于复位状态?

此致、

凯文

您好!

如果 PORz 和 MCU_PORz 为低电平、这意味着 TDA4VH 器件处于复位状态。

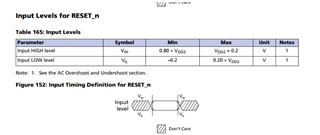

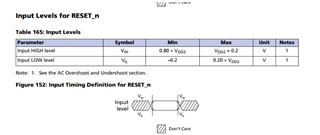

在 TDA4结束复位后、作为 DDRSS 和 LPDDR4初始化序列的一部分、LPDDR4存储器的 RESET_n 应驱动为低电平(以复位存储器)。 您提供的原理图显示 RESET_n 具有弱下拉电阻器、该电阻器应在被 TDA4器件驱动为低电平之前将信号保持在低电平。 因此、我不是很清楚为什么要观察到 RESET_n 为高电平。 也许可以检查 PCB 上是否安装了 R701、而不是 R702?

通常、RESET_n 应为低电平、同时 LPDDR4的电压应斜升。

此致、

凯文