主题中讨论的其他器件: SK-AM64B、 AM6442

工具与软件:

你(们)好

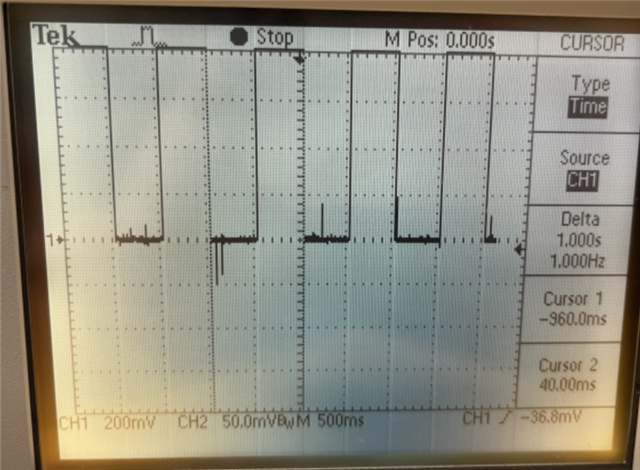

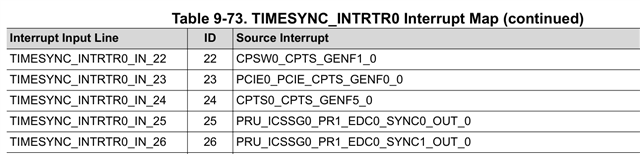

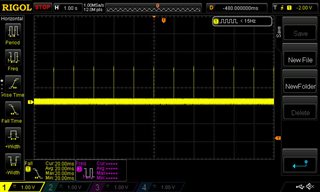

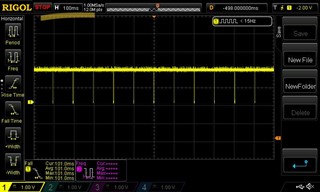

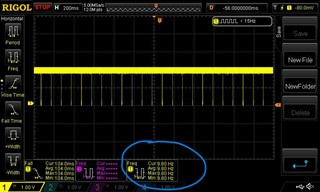

我们在重新启用后观察 PPS 的一些奇怪频率( 回波1 >/sys/class/ptp/ptp0/pps_enable;回 波0 >/sys/class/ptp/ptp0/pps_enable;回波 1 >/sys/class/ptp/ptp0/pps_enable )。 该信号在 GPIO1_37 (V5)输出上测量。

为什么会这样?

您可能会看到、在重新启用 PPS 信号后、信号周期约为100ms.s

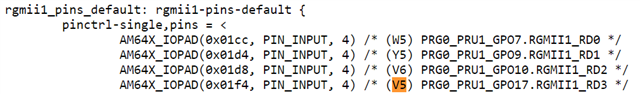

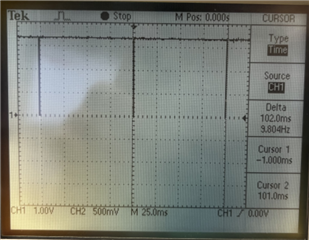

在设备树中有这样的配置:

&cpsw3g {

pinctrl-names = "default";

pinctrl-0 = <&cpsw_mdio0_pins_default

&rgmii1_io_bus_pins_default

&rgmii2_service_pins_default

>;

cpts@3d000 {

ti,pps = <7 1>;

};

};

#define TS_OFFSET(pa, val) (0x4+(pa)*4) (0x10000 | val)

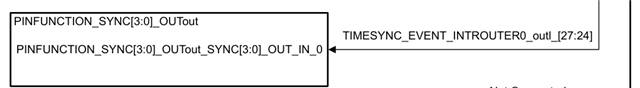

×ync_router {

pinctrl-names = "default";

pinctrl-0 = <&mcu_cpts_pps>;

/* Example of the timesync routing */

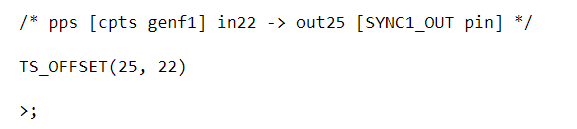

mcu_cpts_pps: mcu-cpts-pps {

pinctrl-single,pins = <

/* pps [cpts genf1] in22 -> out37 [cpts hw8_push] */

TS_OFFSET(37, 22)

/* pps [cpts genf1] in22 -> out25 [SYNC1_OUT pin] */

TS_OFFSET(25, 22)

>;

};

};