工具与软件:

TI exprits、您好!

在 BYD SA5中,我们遇到了一个非常奇怪的问题,我们配置了主域 MSRam,

在前面的数据包中、我们已经提到了这一点。

我们在0x80000中放置了一些文本段、我们在 RAT 函数中绑定了该文本段

#define CSL_MCU_ARMSS_RAT_CFG_BASE (0x40f90000UL)

#define MSRAM_RAT_REGION_INDEX 10U

#define MSRAM_RAT_REGION_BASE (0x4F02000000UL)

#define MSRAM_RAT_REGION_SIZE (0x80000UL)

#define MSRAM_RAT_REGION_LOCAL_BASE (0x80000UL)

void Rat_Msram512KBInit(void)

{

bool ratRetVal;

CSL_RatTranslationCfgInfo translationCfg;

uint32_t index = MSRAM_RAT_REGION_INDEX;

/* Add RAT configuration to access address > 32bit address range */

translationCfg.translatedAddress = MSRAM_RAT_REGION_BASE;

translationCfg.sizeInBytes = MSRAM_RAT_REGION_SIZE;

translationCfg.baseAddress = (uint32_t)MSRAM_RAT_REGION_LOCAL_BASE;

ratRetVal = CSL_ratConfigRegionTranslation((CSL_ratRegs *)CSL_MCU_ARMSS_RAT_CFG_BASE,

index, &translationCfg);

if (ratRetVal == false) {

UART_printf("\nFailed to configure the RAT index %d address 0x%lx\n", index, translationCfg.translatedAddress);

}

}

00080000 00080000 00033020 00033020 rwx 00080000 00080000 00033020 00033020 rwx .main_Msram

但目前我们做了一些压力测试,发现,有时 SBL 将数据从临时存储器复制到主域 msram

某些文本在主域 MSARAM 中不正确、但 DDR 和 MCU msam 中的文本都是正确的。

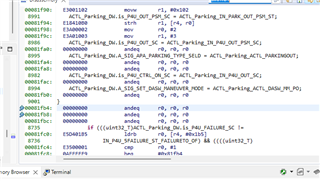

如 0x81fb4中的文本应为

正确数据就像波纹管一样

81f9c: 03 10 a0 e3 mov r1, #3

; ACTL_Parking_DW.is_P4U_OUT_SC = ACTL_Parking_IN_P4U_OUT_PSM_SC;

81fa0: c1 01 c4 e5 strb r0, [r4, #449]

; ACTL_Parking_DW.A_SIG_APA_PARKING_TYPE_SELD = ACTL_Parking_ACTL_PARKINGOUT;

81fa4: a5 01 c4 e5 strb r0, [r4, #421]

81fa8: 01 00 a0 e3 mov r0, #1

; ACTL_Parking_DW.is_P4U_CTRL_ON_SC = ACTL_Parking_IN_P4U_OUT_SC;

81fac: b1 11 c4 e5 strb r1, [r4, #433]

; ACTL_Parking_DW.A_SIG_SET_DASW_MANEUVER_MODE = ACTL_Parking_ACTL_DASW_MM_PO;

81fb0: 9c 01 c4 e5 strb r0, [r4, #412]

; }

81fb4: 34 d0 8d e2 add sp, sp, #52

81fb8: f0 8f bd e8 pop {r4, r5, r6, r7, r8, r9, r10, r11, pc}

81fbc: 00 f0 20 e3 nop

; if (((uint32_T)ACTL_Parking_DW.is_P4U_FAILURE_SC !=

81fc0: b5 01 d4 e5 ldrb r0, [r4, #437]

; IN_P4U_5FAILURE_ST_FAILURETO_OF) && ((((uint32_T)

81fc4: 01 00 50 e3 cmp r0, #1

我直接读取存储器、发现从0x81fa0到0x81fbc 有32个字节已更改为0、

我们还检查主域 MSRAM 中的文本、

有许多地方已经改变了

如这里所示

如这里所示

如这里所示

所有更改的大小为32字节、应该是文本代码、但变为0、是否存在高速缓存问题或 DMA 问题?

我们可以将主域 SRAM 用于 MCU 文本代码吗? 您能否说明一下在 MCU 域中使用主域 MSRAM 的方法没有问题、您能否就此向您的 IP 设计团队核实。