Other Parts Discussed in Thread: SYSCONFIG

主题中讨论的其他器件:SysConfig

工具与软件:

每个 PRU_ICSSG PRU 处理器都通过其 R30寄存器实现快速 GPO、通过 R31寄存器实现快速 GPI。 AM64x/AM243x 具有20个引脚输出 PRU GPIO 引脚、该器件使用不同的多路复用模式将所有 GPI 信号及其相应的 GPO 信号多路复用到同一引脚上。

如何从 PRU 固件代码在 GPO 和 GPI 操作之间切换?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: SYSCONFIG

工具与软件:

每个 PRU_ICSSG PRU 处理器都通过其 R30寄存器实现快速 GPO、通过 R31寄存器实现快速 GPI。 AM64x/AM243x 具有20个引脚输出 PRU GPIO 引脚、该器件使用不同的多路复用模式将所有 GPI 信号及其相应的 GPO 信号多路复用到同一引脚上。

如何从 PRU 固件代码在 GPO 和 GPI 操作之间切换?

适用于 AM64x 和 AM243x 的 PRU GPIO 双向模式

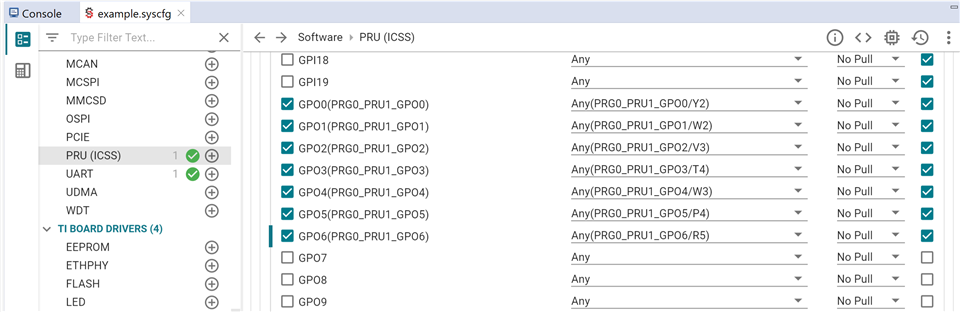

我们可以在双向模式下对 PRU GPIO 引脚进行编程、以便能够从 PRU 在 GPO 和 GPI 操作之间切换。 GPO/GPI 引脚的特殊 I/O 引脚连接是 是使用 IEP EDIO 信号控制实现的 使用单个 SoC 电平引脚多路复用模式来提供输入/输出切换。

IEP EDIO 接口具有32个数据输出使能(DATA_OUT_EN)信号、对应于其32个数据输入和32个数据输出信号。 在器件上、每个 PRU_ICSSG 模块的 IEP0 EDIO (没有 IEP1 EDIO) I/O 中只有4个引脚输出(PRG[2:0]_IEP0_EDIO_DATA_IN_OUT[31:28])。

当为配置 I/O 引脚时、未使用的输出使能可选择重新用作 GPO 使能、从而允许每个 ICSSG GP 引脚用作 GPO 或 GPI GPO 多路复用模式 . 一组 SoC 电平寄存器(CTRLMMR_ICSSG[2:0]_CTRL[2:0])用于确定每个 GPO 模式引脚的行为。

默认情况下、[19-0]GPM_Bidi 位字段设置为0h、相应的 GPO 引脚仅在选择 GPO 多路复用模式时作为输出运行。 相应的 GPI 信号(ICSSG GPI[19:0]输入)被驱动为低电平。

当寄存器的[19-0]GPM_Bidi 位字段设置为1h 时、相应的 ICSSG_DIGIO_DATA_OUT_EN_REG[31-0] DATA_OUT_EN 位字段用于控制 GPO 输出缓冲区。

在 PRU IO 空项目中启用双向模式的步骤:

导入 CCS 工程、

修改 R5F 项目-

修改 PRU 项目-

以下代码启用 PRU GPIO[6-0]的双向功能并将 GPO3转换为 GPI3。 将 main.asm 文件中的寄存器空间(零&r0120)清除后出现的代码替换为以下代码。

PIN_CONTROL:

;Unlock CTRLMMR kick protection registers

ldi32 TEMP_REG, 0x68EF3490

ldi32 CTRL_REG, 0x43001008

sbbo &TEMP_REG, CTRL_REG, 0, 4

ldi32 TEMP_REG, 0xD172BC5A

ldi32 CTRL_REG, 0x4300100C

sbbo &TEMP_REG, CTRL_REG, 0, 4

ldi32 TEMP_REG, 0x68EF3490

ldi32 CTRL_REG, 0x43005008

sbbo &TEMP_REG, CTRL_REG, 0, 4

ldi32 TEMP_REG, 0xD172BC5A

ldi32 CTRL_REG, 0x4300500C

sbbo &TEMP_REG, CTRL_REG, 0, 4 ;Set bits 0-6 of CTRLMMR_ICSSG0_CTRL0 to 1 to enable PRU fast GPIO as bidirectional

ldi32 TEMP_REG, 0x7F

ldi32 CTRL_REG, 0x43004100

sbbo &TEMP_REG, CTRL_REG, 0, 4 ;Set bits in IEP_DIGIO_DATA_OUT_EN_REG, GPIO 3 to inputs, rest as outputs

ldi32 TEMP_REG, 0x08

ldi32 EN_REG, 0x2e314

sbbo &TEMP_REG, EN_REG, 0, 4

halt ;end of program

构建和运行示例-

按照此处的步骤- example_pru_empty 来构建和运行该示例

测试功能 -

通过向相应的 R30寄存器位写入1h 并将其外部环回到 GPI3、将其中一个 GPO 引脚设置为高电平。 因此、R31寄存器的值应在 GPI3中接收到高电平信号时发生变化。

其他说明 :解锁 CTRLMMR 保护机制和双向配置是一次性设置,可以在 R5F 侧添加如下所示。

#define KICK0_UNLOCK_VAL (0x68EF3490U)

#define KICK1_UNLOCK_VAL (0xD172BC5AU)

#define CSL_MAIN_LOCK0_KICK0_OFFSET (0x1008)

#define CSL_MAIN_LOCK1_KICK0_OFFSET (0x5008)

void config_CTRLMMR()

{

uint32_t baseAddr;

volatile uint32_t *kickAddr;

volatile uint32_t *regAddr = (volatile uint32_t *)((uint32_t)0x43004100);

baseAddr = (uint32_t)(0x43000000);

/* Lock 0 */

kickAddr = (volatile uint32_t *) (baseAddr + CSL_MAIN_LOCK0_KICK0_OFFSET);

CSL_REG32_WR(kickAddr, KICK0_UNLOCK_VAL); /* KICK 0 */

kickAddr++;

CSL_REG32_WR(kickAddr, KICK1_UNLOCK_VAL); /* KICK 1 */

/* Lock 1 */

kickAddr = (volatile uint32_t *) (baseAddr + CSL_MAIN_LOCK1_KICK0_OFFSET);

CSL_REG32_WR(kickAddr, KICK0_UNLOCK_VAL); /* KICK 0 */

kickAddr++;

CSL_REG32_WR(kickAddr, KICK1_UNLOCK_VAL); /* KICK 1 */

CSL_REG32_WR(regAddr, 0x0000007F); 下面随附了为 PRU GPIO 启用双向模式的修改后 PRU IO 空工程文件。

e2e.ti.com/.../pru_5F00_gpio_5F00_bidirectional_5F00_mode_5F00_enable_5F00_projects.zip