请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TDA4VH-Q1 主题中讨论的其他器件:TDA4VH

工具与软件:

您好!

SDK:8.6

TDA4VH 是否支持在 SPI 模式下的空闲状态下配置 MOSI 引脚电平状态?

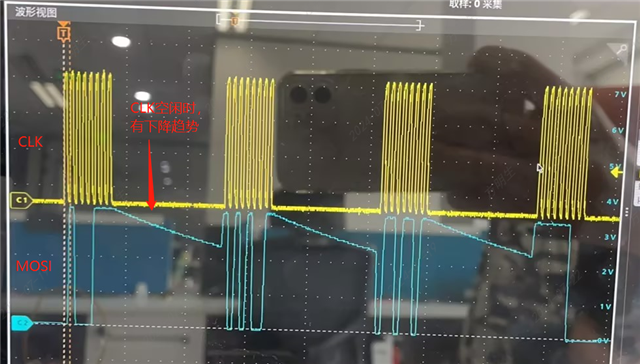

目前、我们在测试中发现、VH 上的 SPI 配置为当 CLK 空闲时将 MOSI 引脚保持在高电平、而发送的另一侧在 MOSI 上有下拉操作、从而产生一个下降波形、如图所示:

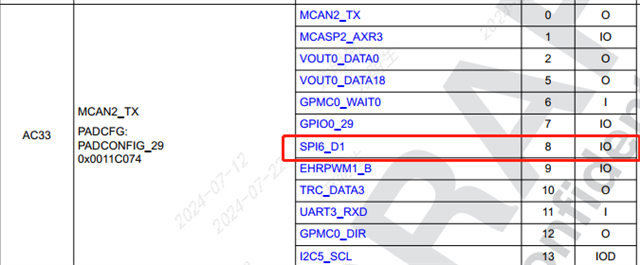

请提供 SPI 模式下 MOSI 引脚默认电平状态的配置方法。