工具与软件:

大家好!

我们的一个客户一直在向 DM 内核固件中添加该功能、同时保留固件构建器包含在此固件中的现有功能。

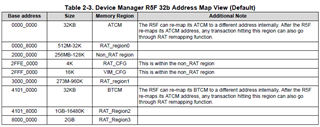

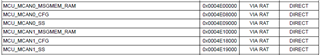

TRM 显示 MCU_MCAN 寄存器可"通过 RAT"访问 DM 内核、我们需要澄清需要如何设置 RAT 才能访问0x04E00000和0x04E10000处的 MCU_MCAN 寄存器。

![]()

针对0x04E00000大小128KB 的当前 syscfg RAT 设置

代码汇总

//Global struct defined

#define CONFIG_ADDR_TRANSLATE_RAT_BASE_ADDR (0x02FFE0000u)

#define CONFIG_ADDR_TRANSLATE_REGIONS (1u)

AddrTranslateP_RegionConfig gAddrTranslateRegionConfig[CONFIG_ADDR_TRANSLATE_REGIONS] =

{

{

.localAddr = 0x4E00000u,

.systemAddr = 0x4E00000u,

.size = AddrTranslateP_RegionSize_128K,

},

};

//Executed Code

AddrTranslateP_Params addrTranslateParams;

AddrTranslateP_Params_init(&addrTranslateParams);

addrTranslateParams.numRegions = CONFIG_ADDR_TRANSLATE_REGIONS;

addrTranslateParams.ratBaseAddr = CONFIG_ADDR_TRANSLATE_RAT_BASE_ADDR;

addrTranslateParams.regionConfig = &gAddrTranslateRegionConfig[0];

AddrTranslateP_init(&addrTranslateParams);

uint32_t mcu_can0_base_addr = (uint32_t)AddrTranslateP_getLocalAddr( (uint64_t)CSL_MCU_MCAN0_MSGMEM_RAM_BASE);

uint32_t mcu_can1_base_addr = (uint32_t)AddrTranslateP_getLocalAddr( (uint64_t)CSL_MCU_MCAN1_MSGMEM_RAM_BASE);

MCAN_isMemInitDone(mcu_can0_base_addr); <----DM core hangs here, in this MCAN driver API call, which reads a register based on above base addr

MCAN_isMemInitDone(mcu_can1_base_addr);

但是、代码似乎无法正确访问 MCU_MCAN 寄存器、并且 MCAN_isMemInitDone () API 由于无法访问 STAT 寄存器而挂起

是否还需要其他东西来将 MCU_MCAN 寄存器空间映射到 DM 内核中?

谢谢!

——Gunter