工具与软件:

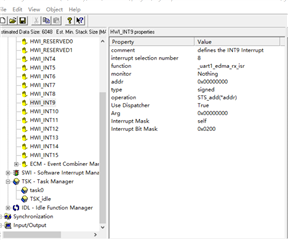

我需要在一个用 DSP/BIOS v5.42.1.9开发的非常旧的项目中添加 UART 驱动程序代码。起初我用 EDMA3把接收到的数据从 UART1的 Rx FIFO 转移到 SRAM 的数据缓冲区中、出现了两个问题、一个是 EDMATC0报告了"读取地址错误"、因为源地址不正确、但我非常确定我在 参数集 RAM 中写入了正确的源地址。 另一个问题是,传输完成中断不能被处理,即使我已经配置了 ISR 在 tcf 文件,如图1所示。

但实际上 IE9没有在核心寄存器 IER 中启用。

BTW,原因 导致 EDMATC0报告"读地址错误",我猜,是片上256k SRAM 作为 L2缓存工作。 我只是取消选中了图片2中显示的内存浏览器中的 L2缓存框,然后 EDMA 运行良好。 但我找不到一个地方可以配置片上256k SRAM 在 gconf.exe 中的工作方式。

因为不知道要解决这两个问题、所以我放弃了尝试使用 EDMA、而只是使用 UART 接收器 ISR 来存储生成的数据。 正如上面遇到的相同问题、无法处理 UART 接收器中断。

我想知道如何配置片上256k SRAM 以在 SRAM (而不是 L2高速缓存)中工作、以及为什么在 gconf.exe 中配置后未设置 IER 中的相应位